# Design and Implementation of High Performance Communication Subsystems for Clusters

# DISSERTATION

Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the

Graduate School of The Ohio State University

By

Mohammad Banikazemi, M.S.

\* \* \* \* \*

The Ohio State University

2000

Dissertation Committee: Approved by

Prof. Dhabaleswar K. Panda, Adviser

Prof. Mario Lauria

Department of Computer and

Information Science

© Copyright by Mohammad Banikazemi 2000

#### ABSTRACT

With the significant increase in computing power of processors and tremendous improvement in the performance of networking hardware, clusters have become a popular platform for high performance computing. In order to make the performance of clusters comparable to that of traditional high performance computing systems, it is crucial to make the communication subsystems of these systems as efficient as possible. In recent years, communication subsystems with user-level protocols have been proposed by the research community and industry to address this issue. All of these communication systems use much simpler communication protocols in comparison with legacy protocols such as the TCP/IP. The role of the operating system has been much reduced in these systems and in most cases user applications are given direct access to the network interface. The Virtual Interface Architecture (VIA) specification has been developed to standardize these user-level protocols and to make their ideas available in commercial systems. The primary objective of this research is to design and implement efficient and high performance communication subsystems for clusters with user-level protocols such that the high performance of the networking technologies is passed to applications. To achieve this goal, this thesis is focused on five components of communication subsystems: network interface support, communication mechanism, distribute shared memory (DSM) support, distributed memory support, and performance evaluation. Several design choices for various components of VIA are proposed and evaluated on different platforms. A prototype implementation of VIA is developed for IBM SP-connected clusters. This implementation remains to be the most efficient software implementation of VIA to date. The performance of this implementation is extensively evaluated and performance bottlenecks have been identified. Furthermore, several hardware enhancements for improving the performance are studied. Design and implementation of the communication infrastructure required for supporting distributed shared memory and distributed memory programming models on top of user-level communication protocols are also studied. The proposed communication mechanisms and their extensive evaluation demonstrate significant potential to be applied to the design of communication subsystems for current and future clusters.

Dedicated to my mother Parvin and my father Hossein

#### ACKNOWLEDGMENTS

I would like to thank my advisor, Prof. D. K. Panda for his invaluable guidance through the course of my graduate study. I am grateful to him for the tremendous time, effort, and wisdom he invested in guiding me and steering my research. More importantly I would like to express my gratitude toward his friendship and understanding during the tough periods of my stay at Ohio State University.

I would like to thank Prof. P. Sadayappan for his support and help as a member of our research group. I thank him for the discussions we had about my research and for his insightful comments. I also thank Prof. M. Lauria for being in my dissertation committee and for his valuable suggestions.

I am grateful to Dr. Bulent Abali of IBM T. J. Watson Research Center and Dr. Rama Govindaraju of IBM for their guidance and friendship both during my internships and afterwards. I am also thankful to Dr. Govindaraju for nominating me for an IBM graduate fellowship award.

I gratefully acknowledge the financial support provided by the Department of Computer and Information Science, National Science Foundation (NSF), an IBM Graduate Fellowship, and a Presidential Fellowship.

I thank Jiuxing Liu, Sencer Kutlug, and Arun Ramakrishnan for their help in running experiments related to Chapters 4 and 5 of this dissertation. It would have been impossible for me to complete this work without their valuable help.

Special thanks go to Darius Buntinas with whom I have spent many hours discussing technical and not so technical topics. I cannot forget his willingness to extend his help under any conditions and at any time. I value his friendship tremendously.

I would also like to thank previous members of the PAC group. In particular, I would like to thank Rajeev Sivaram, Ram Kesavan, Donglai Dai, and Matt Jacunski for hours of discussions on various topics and for their friendship.

I would like to thank the great friends I have made during the course of my stay at Ohio State: Ashkan, Susana, Manfredi, and Neda. Their friendship alone would have made my stay at Ohio State worth while.

Finally, I thank my family, my parents and sister, for their immeasurable love, encouragement, and support. I feel very happy to share with them, the joy of writing this thesis.

# VITA

| 1967                      | . Born - Kashan, Iran                                                                                                                 |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1989                      | . B.S., Electrical Engineering,<br>Isfahan University of Technology,<br>Isfahan, Iran                                                 |

| 1989 - 1994               | Software Engineer and<br>System Administrator,<br>Tehran, Iran                                                                        |

| Winter 1995 - Summer 1996 | . Graduate Teaching Associate,<br>Computer and Info. Science and<br>Electrical Engineering Departments,<br>The Ohio State University. |

| 1996                      | . M.S., Electrical Engineering,<br>Ohio State University                                                                              |

| Fall 1996 - Spring 1997   | . Graduate Teaching Associate,<br>Dept. of Computer and Info. Science,<br>The Ohio State University.                                  |

| Fall 1997 - Spring 1998   | . Graduate Research Associate,<br>The Ohio State University.                                                                          |

| Summer 98                 | Summer Intern, Power Parallel Group, IBM Corporation.                                                                                 |

| Fall 1998 - Spring 1999   | . Graduate Research Associate,<br>The Ohio State University.                                                                          |

| Summer 1999               | . Summer Intern, Research Division, IBM Corporation.                                                                                  |

| Fall 1999 - Spring 2000   | . IBM Graduate Fellow,<br>Ohio State University.                                                                                      |

| Summer 2000 - Fall 2000   | . OSU Presidential Fellow,<br>Ohio State University.                                                                                  |

# **PUBLICATIONS**

#### Research Publications

- M. Banikazemi, B. Abali, L. Herger, and D. K. Panda. "Design Alternatives for VIA and an Implementation on IBM Netfinity NT Cluster." Special issue of Journal of Parallel and Distributed Computing on Cluster and Network-Based Computing, to appear.

- B. Abali, C. B. Stunkel, J. Herring, M. Banikazemi, D. K. Panda, C. Aykanat, and Y. Aydogan. "Adaptive Routing on the New Switch Chip for IBM SP Systems." Special issue of Journal of Parallel and Distributed Computing on Routing in Computer and Communication Networks, to appear.

- M. Banikazemi, D. K. Panda, and P. Sadayappan. "Implementing TreadMarks on Virtual Interface Architecture (VIA): Design Issues and Alternatives." Ninth Workshop on Scalable Shared Memory Multiprocessors, held in conjunction with International Symposium on Computer Architecture (ISCA'2000), June 2000.

- M. Banikazemi, V. Moorthy, L. Hereger, D. K. Panda, and B. Abali. "Efficient Virtual Interface Architecture Support for IBM SP Switch-Connected NT Clusters." *International Parallel and Distributed Processing Symposium (IPDPS'2000)*, pp. 33-42, May 2000.

- M. Banikazemi, C. Stunkel, D. K. Panda, and B. Abali. "Adaptive Routing in RS/6000 SP-like Bidirectional Multistage Interconnection Networks." *International Parallel and Distributed Processing Symposium (IPDPS'2000)*, pp. 43-52, May 2000.

- M. Banikazemi, B. Abali, and D. K. Panda. "Comparison and Evaluation of Design Choices for Implementing the Virtual Interface Architecture (VIA)." Workshop on Communication and Architectural Support for Network-based Parallel Computing (CANPC-HPCA' 2000).

- M. Banikazemi, R. K. Govindaraju, R. Blackmore, and D. K. Panda. "Implementing Efficient MPI on LAPI for the IBM-SP: Experiences and Performance Evaluation." *International Parallel Processing Symposium (IPPS '99)*, pp. 183–190, April 1999.

- M. Banikazemi, J. Liu, D. K. Panda, and P. Sadayappan. "Implementing TreadMarks over VIA on Myrinet and Gigabit Ethernet: Challenges, Design Experience, and Performance Evaluation." *Technical Report OSU-CISRC-07/00-TR15*.

- M. Banikazemi, J. Liu, S. Kutlug, A. Ramakrishnan, P. Sadayappan, H. Shah, and D. K. Panda. "VIBe: A Microbenchmark Suite for Evaluating Virtual Interface Architecture (VIA) Implementations." *Technical report OSU-CISRC-10/00-TR20*.

M. Banikazemi and D. K. Panda. "Can Scatter Communication Take Advantage of Multidestination Message Passing?." Int'l Symposium on High Performance Computing (HiPC '00), to be

presented.

M. Banikazemi, J. Sampathkumar, S. Prabhu, D. K. Panda, and P. Sadayappan. "Communication Modeling of Heterogeneous Networks of Workstations for Performance Characterization of

Collective Operations." IPPS Heterogeneous Computing Workshop (HCW '99),pp. 125–133, April

1999.

M. Banikazemi, Vijay Moorthy, and D. K. Panda. "Efficient Collective Communication on Heterogeneous Networks of Workstations." *International Conference for Parallel Processing (ICPP'98)*,

pp. 460-467, Aug. 1998.

D. K. Panda, D. Basak, D. Dai, R. Kesavan, R. Sivaram, M. Banikazemi and V. Moorthy. "Simula-

tion of Modern Parallel Systems: A CSIM-Based Approach." 1997 Winter Simulation Conference

(WSC '97), pp. 1013-1020, Dec. 1997.

D. Basak, D. K. Panda, and M. Banikazemi. "Benefits of Processor Clustering in Designing Large

Parallel Systems: When and How?" International Parallel Processing Symposium (IPPS '96), pp.

286-290, Apr. 1996.

# FIELDS OF STUDY

Major Field: Computer and Information Science

#### Studies in:

Computer Architecture Prof. Dhabaleswar K. Panda

Networking Prof. Raj Jain

Operating Systems Prof. Thomas W. Page Jr.

# TABLE OF CONTENTS

|         |                       |                 |                                                       |     |      |     |    |     |    | ]  | Pa | ıge |

|---------|-----------------------|-----------------|-------------------------------------------------------|-----|------|-----|----|-----|----|----|----|-----|

| Abstra  | act .                 |                 |                                                       |     |      |     |    |     |    |    |    | ii  |

| Dedica  | ation                 | 1               |                                                       |     |      |     |    |     |    |    |    | iii |

| Ackno   | wled                  | $_{ m lgments}$ |                                                       |     |      |     |    |     |    |    |    | iv  |

| Vita .  |                       |                 |                                                       |     |      |     |    |     |    |    |    | v   |

| List of | Ta                    | bles            |                                                       |     |      |     |    |     |    |    |    | xi  |

| List of | Fig                   | gures .         |                                                       |     |      |     |    |     |    | •  |    | xii |

| Chapte  | ers:                  |                 |                                                       |     |      |     |    |     |    |    |    |     |

| 1. I    | $\operatorname{ntro}$ | duction         |                                                       |     |      |     |    |     |    |    |    | 1   |

| 1       | 1.1                   | Netwo           | k-Based Computing                                     |     |      |     |    |     |    |    |    | 1   |

| 1       | 1.2                   | Compo           | nents of Communication Subsystems in NBC Environments | ien | ts.  |     |    |     |    |    |    | 3   |

| 1       | 1.3                   | Proble          | n Description                                         |     |      |     |    |     |    |    |    | 4   |

| 1       | 1.4                   | Thesis          | Overview                                              |     |      |     |    |     |    |    |    | 6   |

| 2.      | Com                   | parison         | and Evaluation of Design Choices for Implementing th  | e V | √irt | ual | In | ter | fa | ce |    |     |

| A       | Arch                  | itecture        | (VIA)                                                 |     |      |     | •  |     |    | •  |    | 9   |

| 2       | 2.1                   | Virtua          | Interface Architecture (VIA)                          |     |      |     |    |     |    |    |    | 9   |

|         |                       | 2.1.1           | Overview                                              |     |      |     |    |     |    |    |    | 9   |

|         |                       | 2.1.2           | Message Passing in VIA                                |     |      |     |    |     |    |    |    | 10  |

|         |                       | 2.1.3           | Basic Components of VIA                               |     |      |     |    |     |    |    |    | 11  |

| 2       | 2.2                   | =               | Alternatives                                          |     |      |     |    |     |    |    |    | 11  |

| _       |                       | 2.2.1           | Doorbells                                             |     |      |     |    |     |    |    |    | 11  |

|         |                       | 2.2.2           | Caching Descriptors                                   |     |      |     |    |     |    |    |    | 12  |

|         |                       | 2.2.3           | Address Translation                                   |     |      |     |    |     |    |    |    | 12  |

|         |                       | 2.2.4           | Completion Queues                                     |     |      |     |    |     |    |    |    |     |

|    | 2.3   | Performance Evaluation                                                           | 14         |

|----|-------|----------------------------------------------------------------------------------|------------|

|    |       | 2.3.1 Basic Operations                                                           | 14         |

|    |       | 2.3.2 Caching Descriptors                                                        | 15         |

|    |       | 2.3.3 Address Translation                                                        | 16         |

|    |       | 2.3.4 Completion Queues                                                          | 19         |

|    | 2.4   | Related Work                                                                     | 20         |

|    | 2.5   | Summary                                                                          | 21         |

| 3. | Effic | ient Virtual Interface Architecture Support for IBM SP Switch-Connected NT Clus- |            |

|    | ters  |                                                                                  | 22         |

|    | 3.1   | IBM SP Switch                                                                    | 23         |

|    |       | 3.1.1 Elements of the SP Switch                                                  | 23         |

|    |       | 3.1.2 SP Network Interface Card                                                  | 24         |

|    | 3.2   | Design and Implementation of FirmVIA                                             | 25         |

|    |       | 3.2.1 Requirements and Scope                                                     | 25         |

|    |       | 3.2.2 Design Alternatives and Practical Choices for Implementation               | 26         |

|    | 3.3   | Performance Evaluation                                                           | 30         |

|    |       | 3.3.1 Experimental Setup                                                         | 30         |

|    |       | 3.3.2 Latency                                                                    | 30         |

|    |       |                                                                                  | 33         |

|    |       | ·                                                                                | 35         |

|    | 3.4   | Related Work                                                                     | 37         |

|    | 3.5   | Summary                                                                          | 38         |

| 4. |       | e: A Microbenchmark Suite for Evaluating Virtual Interface Architecture (VIA)    |            |

|    | Impl  | lementations                                                                     | 39         |

|    | 4.1   | Motivation behind a Micro-benchmark Suite for VIA                                | 40         |

|    | 4.2   | VIBe Micro-benchmark Suite                                                       | 41         |

|    |       | 4.2.1 Non-Data Transfer Related Micro-Benchmarks                                 | 41         |

|    |       | 4.2.2 Data Transfer Related Micro-Benchmarks                                     | 42         |

|    |       | 4.2.3 Client/Server Micro-Benchmarks                                             | 45         |

|    | 4.3   | Performance Evaluation                                                           | 45         |

|    |       | 4.3.1 Experiment Testbed                                                         | 46         |

|    |       |                                                                                  | 46         |

|    |       |                                                                                  | 46         |

|    | 4.4   | Summary                                                                          | 48         |

| 5. | Desi  | gn Issues and Alternatives for Supporting Distributed Shared Memory Applications |            |

|    | in C  | lusters                                                                          | 50         |

|    | 5.1   |                                                                                  | 52         |

|    |       | 5.1.1. Coheman av Drote col                                                      | <b>F</b> 9 |

|     |         | 5.1.2 Communication Model and Primitives                            | 53 |

|-----|---------|---------------------------------------------------------------------|----|

|     | 5.2     | Relevant Features of Virtual Interface Architecture (VIA)           | 54 |

|     | 5.3     | Challenges in Designing the Communication Substrate                 | 55 |

|     |         | 5.3.1 Major Issues                                                  | 55 |

|     |         | 5.3.2 Components of the Substrate                                   | 56 |

|     |         | 5.3.3 Connection Management                                         | 56 |

|     |         | 5.3.4 Pre-posting of Receive Descriptors                            | 57 |

|     |         | 5.3.5 Buffer Management                                             | 59 |

|     |         | 5.3.6 Schemes for Handling Asynchronous Messages                    | 60 |

|     | 5.4     | Implementation                                                      | 61 |

|     | 5.5     | Performance Evaluation                                              | 62 |

|     |         | 5.5.1 Experimental Testbed and Setup                                | 62 |

|     |         | 5.5.2 Evaluation of Alternatives for Handling Asynchronous Messages | 63 |

|     |         | 5.5.3 Micro-benchmark-level Evaluation                              | 63 |

|     |         | 5.5.4 Application-Level Evaluation                                  | 64 |

|     | 5.6     | Related Work                                                        | 70 |

|     | 5.7     | Summary                                                             | 70 |

|     | 6.1     | The Native MPI Overview                                             |    |

|     | 6.2     | LAPI Communication Model Overview                                   |    |

|     | 6.3     | Supporting MPI on top of LAPI                                       |    |

|     | 0.0     | 6.3.1 Implementing the Internal Protocols                           |    |

|     |         | 6.3.2 Implementing the MPI Communication Modes                      |    |

|     |         | 6.3.3 A Closer Look at the Implementation of MPI_Send and MPI_Recv  |    |

|     | 6.4     | Optimizing the MPI-LAPI Implementation                              |    |

|     | -       | 6.4.1 The Base MPI-LAPI                                             |    |

|     |         | 6.4.2 MPI-LAPI with Counters                                        |    |

|     |         | 6.4.3 MPI-LAPI Enhanced                                             |    |

|     | 6.5     | Performance Evaluation                                              | 86 |

|     |         | 6.5.1 Latency and Bandwidth                                         | 86 |

|     |         | 6.5.2 NAS Benchmarks                                                |    |

|     | 6.6     | Related Work                                                        |    |

|     | 6.7     | Summary                                                             | 90 |

| 7.  | Con     | clusions and Future Research Directions                             | 92 |

|     | 7.1     | Summary of Research Contributions                                   | 92 |

|     | 7.2     | Suggestions for Future Research                                     |    |

|     |         |                                                                     |    |

| วเน | liogran | n hay                                                               | 06 |

# LIST OF TABLES

| Tab | ole                                                                                                                                                                  | Page |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1 | Cost of basic operations in the Myrinet-Linux and SP-NT testbeds                                                                                                     | . 15 |

| 2.2 | Cost of different methods of implementing the virtual-to-physical address translation (See Figures 1 through 4 for the value of Miss Rate for different benchmarks.) |      |

| 2.3 | Comparison between different approaches for implementing CQs                                                                                                         | . 20 |

| 3.1 | Cost of Basic Operations                                                                                                                                             | . 30 |

| 3.2 | Breakdown of the Host Overhead                                                                                                                                       | . 32 |

| 3.3 | Latency (L in $\mu sec$ ) and Bandwidth (BW in $MBytes/sec$ ) Results of Different VIA Implementations                                                               |      |

| 4.1 | Non-data transfer micro-benchmarks                                                                                                                                   | . 46 |

| 5.1 | Execution statistics for an 8-processor run on TreadMarks with UDP/Ethr communication subsystem                                                                      |      |

| 6.1 | LAPI Functions                                                                                                                                                       | . 76 |

| 6.2 | Translation of MPI communication modes to internal protocols                                                                                                         | . 77 |

| 6.3 | The percentage of improvement for NAS Benchmarks                                                                                                                     | . 90 |

# LIST OF FIGURES

| Fig | gure                                                                                                                                                                                                                                                                                                                    | Page |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

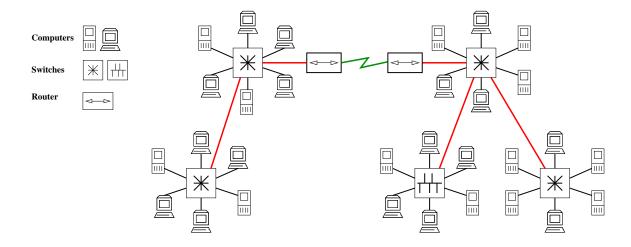

| 1.1 | A Network-Based Computing environment consisting of different types of computers and networking technologies.                                                                                                                                                                                                           | . 2  |

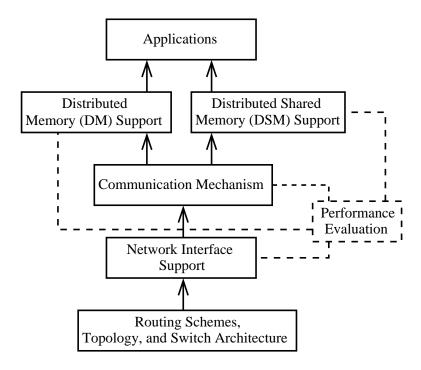

| 1.2 | The components of the communication subsystem in a network-based computing environment                                                                                                                                                                                                                                  | . 3  |

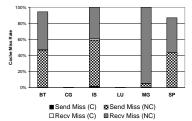

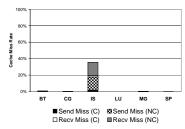

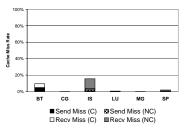

| 2.1 | The cache miss rate for the NAS benchmarks (class A) using four processes (left) and 16 processes (right) with 128-entry direct-mapped caches. C and NC denote compulsory and non-compulsory misses, respectively                                                                                                       | . 18 |

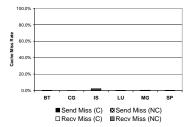

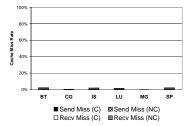

| 2.2 | The cache miss rate for the NAS benchmarks (class A) using four processes (left) and 16 processes (right) with 1024-entry direct-mapped caches and 128-entry 8-way associative caches. (The miss rates are identical for both of these cache types.) C and NC denote compulsory and non-compulsory misses, respectively | . 18 |

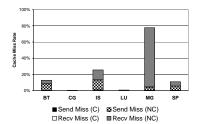

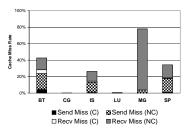

| 2.3 | The cache miss rate for the NAS benchmarks (class B) using 16 processes (left) and 64 processes (right) with 128-entry direct-mapped caches. C and NC denote compulsory and non-compulsory misses, respectively                                                                                                         | . 19 |

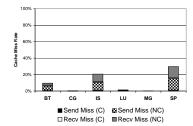

| 2.4 | The cache miss rate for the NAS benchmarks (class B) using 16 processes (left) and 64 processes (right) with 1024-entry direct-mapped caches and 128-entry 8-way associative caches. (The miss rates are identical for both of these cache types.) C and NC denote compulsory and non-compulsory misses, respectively   | . 19 |

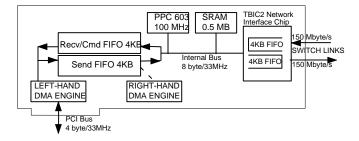

| 3.1 | The Network Interface Card (NIC) architecture in the Netfinity SP system                                                                                                                                                                                                                                                | . 24 |

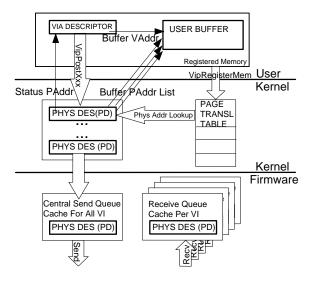

| 3.2 | Sending and receiving messages using Physical Descriptors and address translation                                                                                                                                                                                                                                       | . 28 |

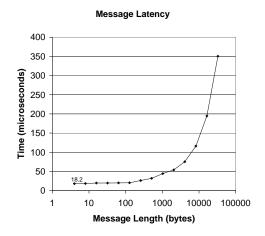

| 3.3 | Message latency for different message sizes                                                                                                                                                                                                                                                                             | . 31 |

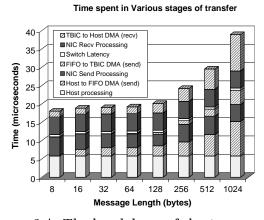

| 3 4 | The breakdown of short message latencies                                                                                                                                                                                                                                                                                | 31   |

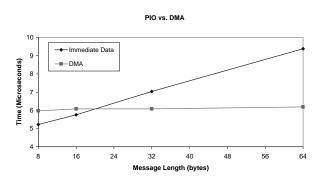

| 3.5  | Delays for sending data with PIO vs. DMA. Descriptor processing delay is included.                                                                                                                                                                                     | 33 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

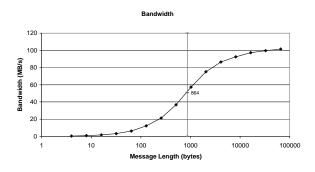

| 3.6  | Measured bandwidth for different message sizes. The half-bandwidth is achieved for 864-byte messages                                                                                                                                                                   | 33 |

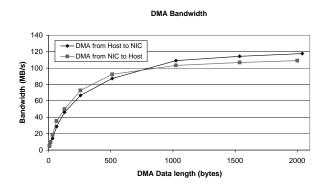

| 3.7  | The raw PCI DMA bandwidth                                                                                                                                                                                                                                              | 34 |

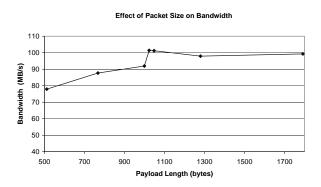

| 3.8  | Effect of packet size on the bandwidth                                                                                                                                                                                                                                 | 35 |

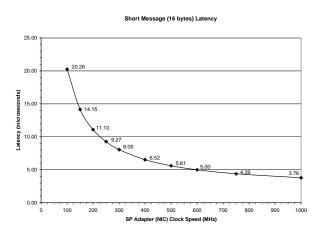

| 3.9  | Impact of NIC cpu speed                                                                                                                                                                                                                                                | 36 |

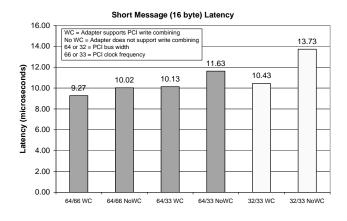

| 3.10 | Impact of PCI speed and width                                                                                                                                                                                                                                          | 36 |

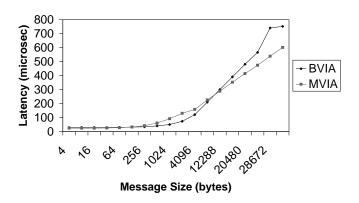

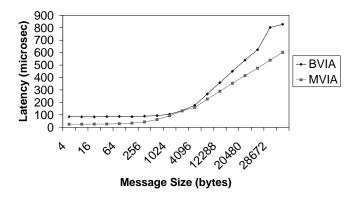

| 4.1  | Basic latency and CPU utilization with polling                                                                                                                                                                                                                         | 47 |

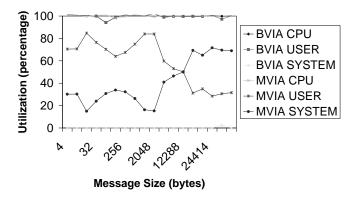

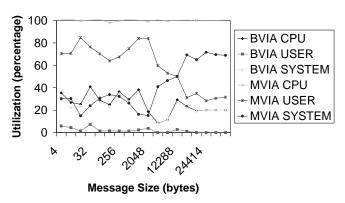

| 4.2  | Basic latency and CPU utilization with blocking                                                                                                                                                                                                                        | 48 |

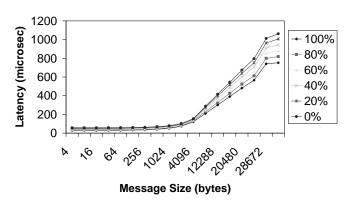

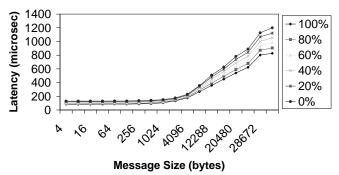

| 4.3  | Latency for varying percentage of send/receive buffer reuse for BVIA with polling. $$ .                                                                                                                                                                                | 49 |

| 4.4  | Latency for varying percentage of send/receive buffer reuse for BVIA with blocking operations.                                                                                                                                                                         | 49 |

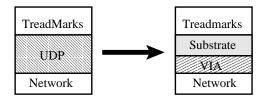

| 5.1  | Goal: designing and implementing a thin communication substrate so that Tread-Marks can run on top of VIA with little overhead. The left stack shows the existing implementation of TreadMarks. The right stack shows the new implementation discussed in this chapter | 51 |

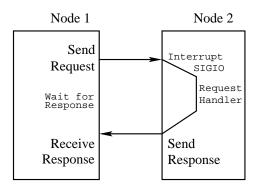

| 5.2  | Request-response communication model used in TreadMarks with UDP support                                                                                                                                                                                               | 53 |

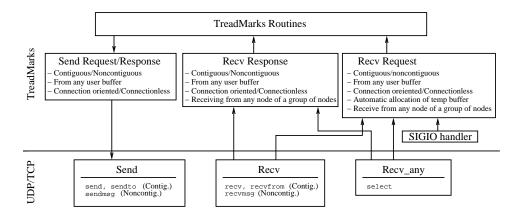

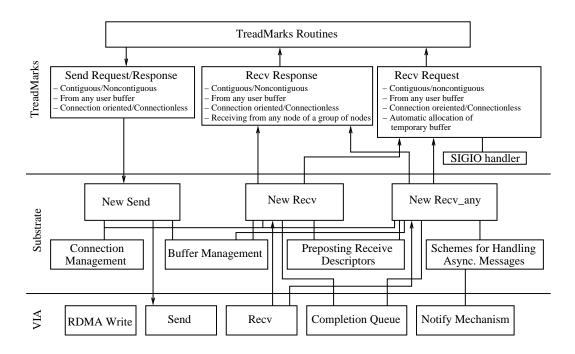

| 5.3  | Four major groups of communication services required by TreadMarks and their implementation using UDP/TCP communication primitives                                                                                                                                     | 54 |

| 5.4  | Services provided by VIA together with their requirements and characteristics                                                                                                                                                                                          | 55 |

| 5.5  | Components of the communication substrate and their relations with VIA services and TreadMarks requirements                                                                                                                                                            | 57 |

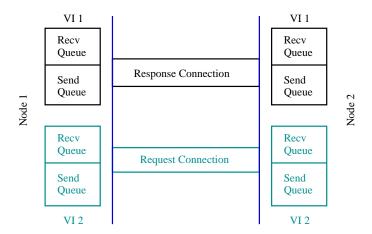

| 5.6  | Proposed connection management scheme with two VI connections between each pair of processes                                                                                                                                                                           | 58 |

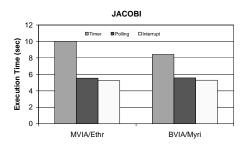

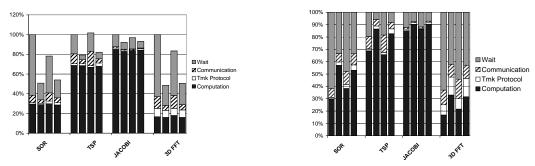

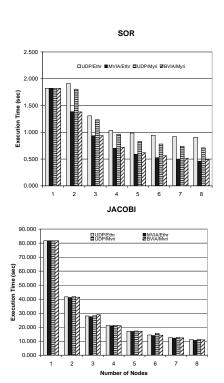

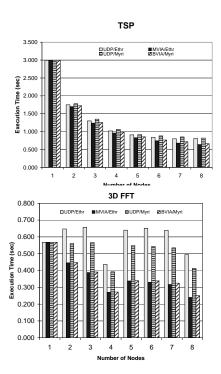

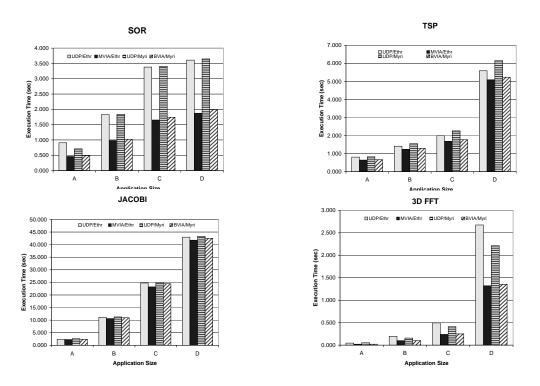

| 5.7  | Performance impact of three alternative approaches (timer, polling, and interrupt) for handling asynchronous messages. Overall execution times for two applications (Jacobi and SOR) on the two VIA communication subsystems (MVIA/Ethr and BVIA/Myri) are shown                                                                                                                                         | 64 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

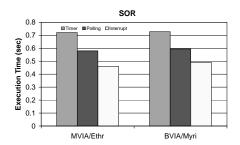

| 5.8  | Performance results of four micro-benchmarks (Barrier, Lock, Page, and Diff). Different cases of Barrier, Lock, and Diff are shown. Barrier (x) indicates the time to achieve a barrier on x nodes. For each of the micro-benchmarks and their individual cases, the four bars (left to right) reflect the time on four different communication subsystems: UDP/Ethr, MVIA/Ethr, UDP/Myri, and BVIA/Myri | 65 |

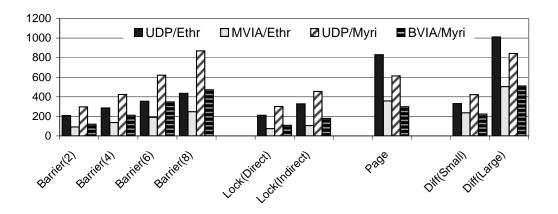

| 5.9  | Overall execution times and their breakdowns for four applications on four implementations. For each application, the bars from left to right represent the results for UDP/Ethr, MVIA/Ethr, UDP/Myri, and BVIA/Myri communication subsystem, respectively. The left graph shows times normalized to the UDP/Ethr time. The right graph shows the percentage breakdown of different components           | 66 |

| 5.10 | Execution times for four applications on four different communication subsystems as the number of nodes are varied from 1 to 8. The bars from left to right (for a given number of nodes) represent results for UDP/Ethr, MVIA/Ethr, UDP/Myri, and BVIA/Myri, respectively                                                                                                                               | 68 |

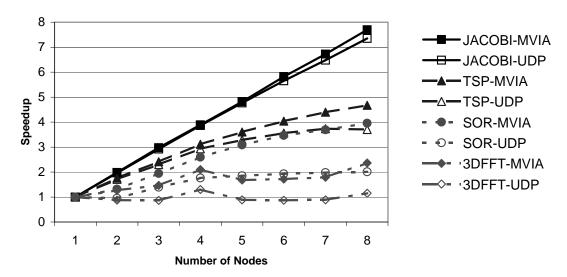

| 5.11 | Speedups for the four applications on different number of nodes for MVIA/Ethr and UDP/Ethr (on Gigabit Ethernet)                                                                                                                                                                                                                                                                                         | 69 |

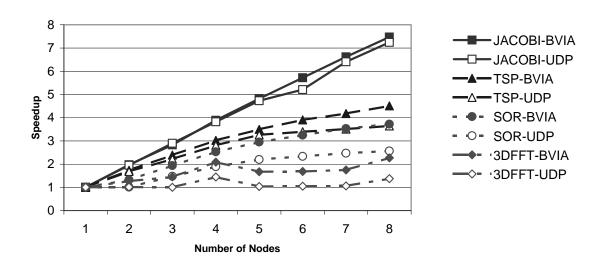

| 5.12 | Speedups for the four applications on different number of nodes for BVIA/Myri and UDP/Myri (on Myrinet)                                                                                                                                                                                                                                                                                                  | 69 |

| 5.13 | Effect of application size on execution times of applications with different problem sizes. The respective problem sizes $(A, B, C, and D)$ are presented in the text. For each application size, the bars from left to right represent the results for UDP/Ethr, MVIA/Ethr, UDP/Myri, and BVIA/Myri communication subsystem, respectively.                                                              | 70 |

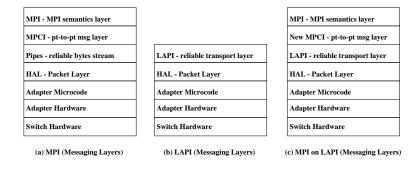

| 6.1  | Protocol Stack Layering                                                                                                                                                                                                                                                                                                                                                                                  | 73 |

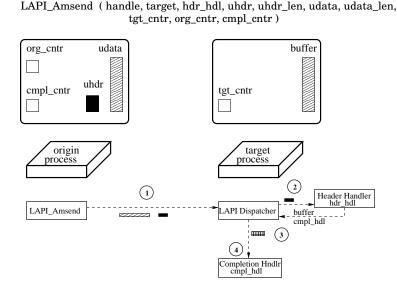

| 6.2  | LAPI overview                                                                                                                                                                                                                                                                                                                                                                                            | 75 |

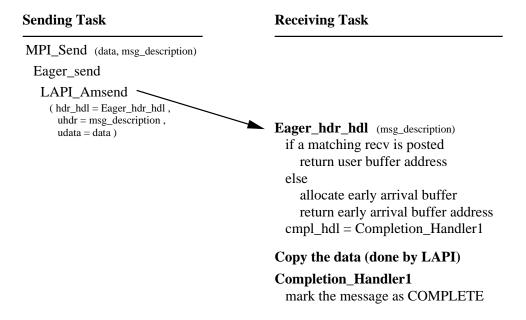

| 6.3  | Outline of the Eager protocol: (a) Eager send, (b) the header handler for the Eager send and (c) the completion handler for the Eager send                                                                                                                                                                                                                                                               | 78 |

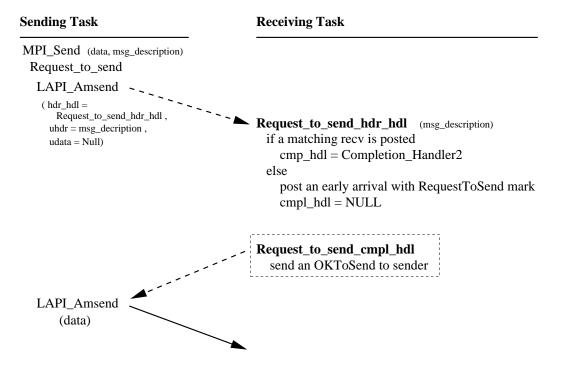

| 6.4  | Outline of the first phase of the Rendezvous protocol: (a) Request to Send, (b) The Header handler for the request to send and (c) the completion handler for the request to send.                                                                                                                                                                                                                       | 79 |

| 6.5  | Outline of the standard send for messages shorter than the Eager Limit and the ready-mode send                                                            | 80 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.6  | Outline of the standard send for messages longer than the Eager Limit and the synchronous-mode send                                                       | 80 |

| 6.7  | Outline of receive for messages sent using the Rendezvous protocol                                                                                        | 81 |

| 6.8  | Outline of the buffered-mode send                                                                                                                         | 81 |

| 6.9  | Outline of receive for messages sent by the Eager protocol                                                                                                | 81 |

| 6.10 | Outline of MPI_Send and the sequence of actions taken at the sending and receiving tasks when the message size is less than the Eager Limit               | 82 |

| 6.11 | Outline of MPLSend and the sequence of actions taken at the sending and receiving tasks when the message size is equal to or greater than the Eager Limit | 83 |

| 6.12 | Outline of MPI_Recv                                                                                                                                       | 84 |

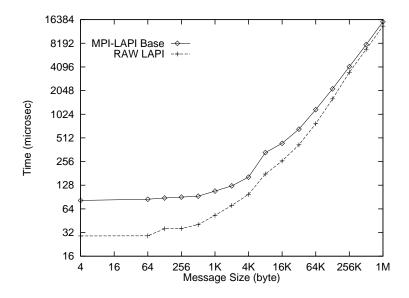

| 6.13 | Comparison between the performance of raw LAPI and MPI-LAPI                                                                                               | 85 |

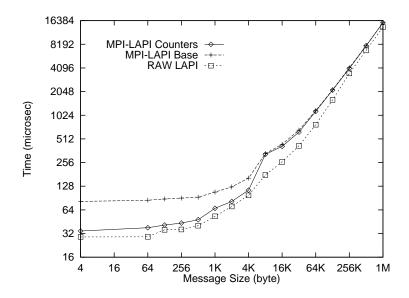

| 6.14 | Comparison between the performance of raw LAPI and improved version of MPI-LAPI                                                                           | 86 |

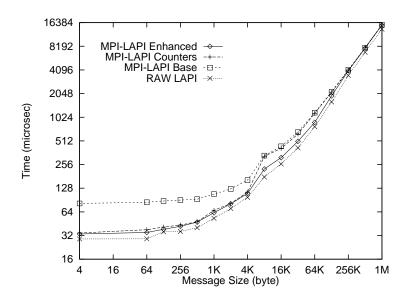

| 6.15 | Comparison between the performance of raw LAPI and different versions of MPI-LAPI.                                                                        | 87 |

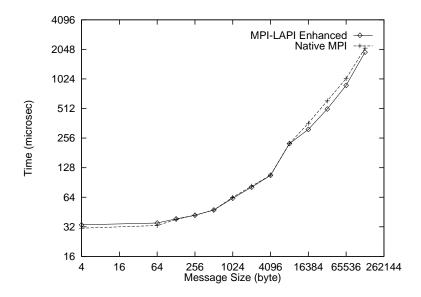

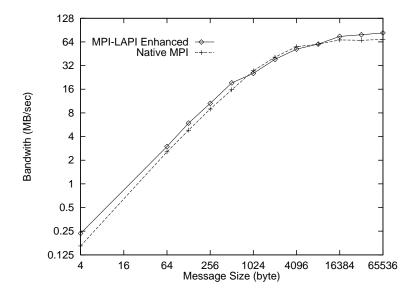

| 6.16 | Comparison between the performance of the native MPI and MPI-LAPI                                                                                         | 88 |

| 6.17 | Comparison between the performance of the native MPI and MPI-LAPI                                                                                         | 88 |

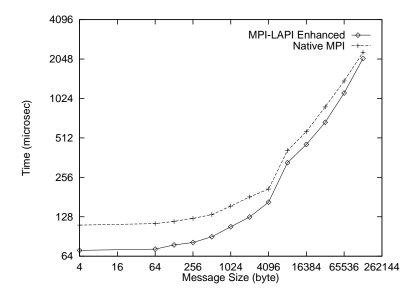

| 6.18 | Comparison between the performance of the native MPI and MPI-LAPI in interrupt mode.                                                                      | 89 |

#### CHAPTER 1

#### INTRODUCTION

## 1.1 Network-Based Computing

Network-Based Computing (NBC) is becoming increasingly popular for providing cost-effective and affordable parallel computing for day-to-day computational needs [10, 31, 52]. Such environments consist of clusters of workstations connected by System, Local, or Wide Area Networks (SANs, LANs, or WANs). Figure 1.1 illustrates such an environment. The major advantage of the NBC environments over traditional high performance computing platforms (such as massively parallel processors (MPPs)) is their lower cost. Although the cost of a group of workstations connected to each other through available networking technologies has been always much less than the cost of an MPP with the same number of nodes, the major obstacles in the usage of clusters as high performance computing platforms has been the limitation of the available networking technologies (in terms of achievable latency and bandwidth). The introduction and mass production of high bandwidth networking technologies such as Myrinet [22], Fast Ethernet, Gigabit Ethernet, FDDI, and ATM [11] has made clusters and Networks of Workstations (NOWs) a viable alternative platform for high performance computing. A wide variety of systems have recently emerged to create a new class of computing platforms for high performance computing. Systems from the Beowulf clusters of Linux PCs interconnected through Ethernet or Myrinet networking technologies to clusters of RS6000 workstations interconnected by SP switches [50, 8] fall into this new class of computing platforms. However, since the new hardware and software networking technologies have not been primarily developed for high performance computing, the communication overhead seen by high performance applications can be too high to make them directly usable for this branch of computing. In order to make the performance of clusters comparable to that of traditional high performance computing systems, it is crucial to make the communication subsystems of these systems as efficient as possible.

A portable programming environment [29] is also key to the success of high performance computing systems. Over the last few years, researchers have developed standard interfaces such as PVM [52, 57] and Message Passing Interface (MPI [23, 39, 40]) to provide portability for the parallel programs written in distributed memory programming model. These interfaces and standards do not force an application developer to understand the intricate details of the hardware, software, and network characteristics. However, the performance of applications depends heavily on the latency and bandwidth required for interprocessor communication and synchronization across the nodes as seen by applications developed by using these standards.

In recent years, the MPI standard has become the most popular and widely used standard for developing message passing high performance applications. Many older applications have been

Figure 1.1: A Network-Based Computing environment consisting of different types of computers and networking technologies.

rewritten using the communication primitives as defined by the MPI standard. New applications are mostly being written by using this standard as well. The MPI standard defines a set of functions for point-to-point communications. In the earlier versions of MPI (Versions 1.0 and 1.1), all point-to-point operations were two-sided operations. In these operations, for every send operation there should exist a corresponding receive operation. In the latest version of the MPI standard (Version 2.0), one-sided operations have been provided too. One sided operations (also known as Remote Memory Access operations) extend the communication mechanisms of MPI by allowing one process to specify all communication parameters, both for the sending side and for the receiving side [40]. In addition to point-to-point operations, MPI defines a rich set of collective operations (such as broadcast, barrier synchronization, gather, and reduction). Collective communication is defined as communication that involves a group of processes. Many parallel applications make extensive use of such collective communications.

The distributed shared memory (DSM) programming model [29] is another programming model used in developing parallel applications. In order to support applications developed in this model, the communication subsystem should provide the required facilities to maintain a coherent view of the shared memory by all application processes running across different computing nodes of a cluster. The performance of this type of applications will heavily depend on the performance of the underlying communication subsystems.

In order to achieve an acceptable performance (comparable to the performance of MPPs) in NBC environments, having efficient communication and synchronization services is crucial. Furthermore, the high performance of the communication subsystem should be passed to the applications, if NBC systems are to become a viable choice for high performance computing.

The remaining part of this chapter is organized as follows. Different components of communication subsystems in NBC environments are discussed in Section 1.2. The description of the problem this research aims to solve is presented in Section 1.3. The overview of this thesis is presented in Section 1.4.

# 1.2 Components of Communication Subsystems in NBC Environments

Designing an efficient communication subsystem requires a comprehensive study of different components of the communication subsystem and the interaction between these components. We divide the communication subsystem into several layers based on the functional and architectural characteristics of the components. Figure 1.2 shows the different components of the communication subsystem in an NBC environment used for high performance computing.

Figure 1.2: The components of the communication subsystem in a network-based computing environment.

The bottom most layer consists of the interconnection topology, switching technology, and routing schemes. As shown in Fig. 1.1, the topology of the interconnection network in an NBC system is typically irregular. In general, such a system can be a WAN consisting of several LANs connected to each other through possibly different networking technologies. Switching elements are responsible for forwarding packets from one link to another one. They perform the forwarding of packets by using techniques such as store-and-forward and cut-through. Given the source and destination of a message, the routing scheme determines the path (links) the message takes. The routing scheme must also provide a mechanism for deadlock avoidance or recovery.

The next layer in the communication subsystem is called network interface support. The network interface at the host typically has a processor, memory and a few DMA engines. DMA engines are used to transfer the packets between the host memory and the interface memory and between the interface memory and the network. Modern network interfaces are programmable and can have a significant role in reducing the communication load of host processors.

The next layer in Fig. 1.2 is called the communication mechanism. This layer is responsible for transmitting the data from a source node to a destination node. This layer is also responsible for adding the required header information to the message. The communication mechanism layer deals also with the fragmentation (packetization) and re-assembly of messages at sending and receiving sides. This layer may enforce the ordering among messages and may guarantee the reliable delivery of data.

The communication mechanism layer is used to implement two components of the next layer: 1) distributed memory support for the programs written in this model by providing communication and synchronization services, and 2) distributed shared memory support for DSM programs by providing the required infrastructure for coherence protocols.

The performance evaluation component as shown in Fig. 1.2 is used for evaluation and tuning of different components of the communication subsystem. It is crucial that the performance of different components and alternative choices for their implementation are evaluated such that the implementation can be tuned for the best performance. Furthermore, the performance evaluation can be used for identifying software and hardware approaches that can be used to eliminate the performance bottlenecks.

# 1.3 Problem Description

The primary objective of this research is to design and implement efficient and high performance communication subsystems for Network-Based Computing environments with SAN/LAN technologies which are also known as Clusters such that the high performance of the networking technologies is passed to applications. To achieve this goal, this thesis is focused on five major components of communication subsystems (depicted in Fig. 1.2): network interface support, communication mechanism, DSM support, distributed memory support, and performance evaluation components. In the rest of this section, we explain the challenges involved in achieving such a goal and present the specific problems this research addresses.

Raw bandwidth of networks have increased significantly in the past few years and networking hardware supporting bandwidths in the order of gigabits per second have become widely available. However, the traditional networking architectures and protocols do not reach the performance of the hardware at the application level. The layered nature of the legacy networking softwares and the usage of expensive system calls and extra memory–to–memory copies required in these systems are some of the factors responsible for degradation of the communication subsystem performance as seen by the applications. In recent years, user-level communication subsystems [29] such as AM [55], VMMC [21], FM [42], U-Net [54, 56], LAPI [45], and BIP [43] have been proposed by the research community and industry to address these issue. All of these communication systems use much simpler communication protocols in comparison with legacy protocols such as the TCP/IP. The role of the operating system has been much reduced in these systems and in most cases user applications are given direct access to the network interface.

The Virtual Interface Architecture (VIA) specification has been developed to standardize these user-level network interfaces and to make their ideas available in commercial systems [7]. However, the flexibility of the VIA specification has left several choices viable for the implementation of various components of VIA. These design choices should be identified and evaluated. The impact of network interface support on the performance of these components and the overall performance of the communication subsystem needs to be investigated. Whether a framework for evaluating different implementations of VIA can be developed is an important question which should be addressed.

The main goal of providing high performance (low latency and high bandwidth) communication subsystems is to make such a performance available at the user application level. If only a small fraction of the low latency and high bandwidth provided by the communication subsystem (such as VIA and LAPI) becomes available at the application level, the main purpose of using efficient communication subsystems has been practically defeated. As mentioned earlier, distributed memory and DSM are the two major programming paradigms used for high performance computing. Therefore, it is crucial to provide the performance of the underlying communication subsystems to the applications written in either of these programming models.

Specifically, this thesis looks at the following problems:

- 1. How different components of VIA can be designed and developed with respect to modern network interface cards?

- 2. How these components can be used to build VIA in the most efficient manner?

- 3. Can a set of micro-benchmarks be used for evaluating different implementations of VIA?

- 4. How DSM applications can take advantage of high performance user-level communication protocols such as VIA?

- 5. How the high performance and efficiency of user-level communication protocols such as LAPI can be passed to distributed memory applications?

Let us look at these problems and the associated challenges in detail.

## • Design, Implementation, and Evaluation of VIA Components:

As mentioned earlier in this chapter, VIA is made of several components. In order to implement VIA in the most efficient manner, various approaches for developing these components should be studied, implemented, and evaluated. Virtual-to-physical address translation, doorbells, and completion queues are among the major components whose implementations are extremely important. How the network interface support can be utilized to implement these components in the most efficient manner is also an important issue which should be addressed.

Approaches for implementing the virtual-to-physical address translation component should address two major questions: 1) which agent is responsible for performing the translation (i.e. the host processor or the Network Interface Controller (NIC)) and 2) where the address translation tables are stored. VIA doorbells can be implemented in software or hardware. Both software and hardware approaches for implementing doorbells should be studied and evaluated. Similarly, software and hardware implementations of completion queues should be proposed and evaluated.

# • Design and Implementation of VIA:

After different design choices for VIA components are evaluated, it is important to show how these components can be put together in order to achieve the lowest latency and highest bandwidth possible. The impact of software and hardware restrictions and limitations on any given platform needs to be taken into account. The division of the work between different units such as the host processor and the NIC may have a significant impact on the overall performance of the communication subsystem. Considering the imbalance in processing power of these units, it is crucial that units with smaller computing power are not overloaded by performing too many operations. Furthermore, the performance of the implementation needs

to be evaluated in a comprehensive manner such that the factors limiting the performance can be identified.

# • Framework for Evaluating VIA Implementations:

Considering the importance of VIA and its potential for becoming the standard communication protocol for clusters, providing a systematic method for evaluating different implementations of VIA is of utmost importance. However, no such method is currently available. A suite of micro-benchmarks can be used for this purpose. Such a suite of micro-benchmarks can be used not only for the evaluation of different implementations of VIA, but also for pinpointing performance bottlenecks and possible approaches for alleviating them. Furthermore, such a suite of micro-benchmarks can be used by designers of higher communication layers to achieve the best performance by taking into account the performance of different VIA features.

#### • Efficient Shared Memory Support for DSM Applications:

DSM applications rely on a global shared address space across different machines. Softwares such as TreadMarks [36, 9] provide such a view and hide from the applications the communication operations required for providing a coherent view of the shared address space. These systems usually use legacy protocols such as UDP and TCP for the required communications. It is important to take advantage of the high performance of user-level communication protocols to perform the required communication operations in the most efficient manner. The request/reply model used in Software DSM (SDSM) systems such as TreadMarks requires the communication subsystem to deal with unexpected requests. Therefore, using an efficient mechanism for notifying the system of the arrival of requests is crucial. Connection management, buffer management, and support for unexpected messages are among other issues which should be studied.

#### • Efficient Message Passing Facility for Distributed Memory Applications:

In order to pass the high performance of the communication subsystem to the distributed memory applications, the communication primitives as defined in standards such as MPI should be implemented in terms of the low level primitives provided by the underlying communication subsystem. It is crucial to keep the overhead of these implementations as low as possible such that the high performance associated with the communication networks and low-level messaging libraries become available to the applications. The most important issue in implementing standards such as MPI is avoiding any unnecessary data copies. Another important issue is that in MPI, received messages can be matched with posted receives in an out-of-order fashion. Providing such a feature without using extra data copies is another challenge.

#### 1.4 Thesis Overview

Having examined the research issues in the design of efficient communication subsystems for clusters, we now present an overview of our solutions. We focus on improving the performance of applications in cluster environments along five major directions as discussed in Section 1.3.

Chapter 2 focuses on different design issues involved in implementing a high bandwidth, low latency communication subsystem. We evaluate and compare the performance of different implementations of essential VIA components. We discuss the advantages and disadvantages of each design approach and describe the required network interface support for implementing each of

them. In particular, different possible approaches for implementing components such as software doorbells, virtual-to-physical address translation, and completion queues are discussed. We use NAS Parallel Benchmarks [6] to study the effect of caching the address translation tables on the NIC and to study design issues involved in implementing completion queues. We consider two platforms: IBM Netfinity SP cluster running the NT 4.0 operating system and a Myrinet connected cluster of PCs running the Linux operating system. We identify the best choices for implementing each of these components on both of these platforms.

In Chapter 3, we look at a prototype implementation of VIA for SP-connected NT clusters. We use the results presented in Chapter 2 and show how different components of a communication subsystem can be put together in order to achieve the lowest latency and highest bandwidth possible. In particular, we explain how the virtual-to-physical address translation can be implemented efficiently with a minimum Network Interface Card (NIC) memory requirement. We show how caching the VIA descriptors on the NIC can reduce the communication latency. We also present an efficient scheme for implementing the VIA doorbells without any hardware support. A comprehensive performance evaluation study of the implementation is provided. The performance of the implemented VIA surpasses that of other existing software implementations of the VIA and is comparable to that of a hardware VIA implementation. The peak measured bandwidth for our system is observed to be 101.4 MBytes/s and the one-way latency for short messages is 18.2 microseconds. We evaluate the performance of our prototype in a comprehensive manner and present the factors limiting the performance. Furthermore, we show how additional hardware support can be used to improve the performance. It is shown that with hardware support for doorbells and a reasonably large amount of NIC memory, it is possible to provide single digit one-way latency with current technology.

VIA has different components (such as doorbells, completion queues, and virtual-to-physical address translation) and attributes (such as maximum transfer unit and reliability modes). Different implementations of VIA lead to different design strategies for efficiently implementing higher level communication layers/libraries (such as Message Passing Interface (MPI [39]). It also has implication on the performance of applications. Currently, there is no framework for evaluating different design choices and for obtaining insight about the design choices made in a particular implementation of VIA and their impact on the performance. In Chapter 4, we address these issues by proposing a new micro-benchmark suite called <u>Virtual Interface Architecture Benchmark</u> (VIBe). This suite consists of several micro-benchmarks which are divided into three major categories: nondata transfer related micro-benchmarks, data transfer related micro-benchmarks, and client/server micro-benchmarks. By using the new benchmark suite, the performance of VIA implementations can be evaluated under different communication scenarios and with respect to the implementation of different components and attributes of VIA. We demonstrate the use of VIBe to evaluate two implementations of VIA (M-VIA and Berkeley VIA). Through these evaluations we show how the VIBe suite can provide insights to the implementation details of VIA and help higher layer software developers.

As mentioned earlier in this Chapter, VIA, as well as other high performance communication subsystems, has a low-level API which provides only the basic communication primitives, it is difficult for user applications to directly use these primitives unless the applications are rewritten. In Chapter 5, we take on a challenge of developing a communication substrate over VIA such that applications using the popular TreadMarks DSM package can take advantage of the enhanced communication performance of VIA. We take a four-step approach in developing the targeted substrate. First, we identify the mismatches between the communication requirements by TreadMarks and

the services provided by VIA. After identifying these mismatches, we propose a set of schemes to eliminate such mismatches. These schemes include connection setup, buffer management, advance posting of descriptors for unexpected messages, and alternative designs to handle asynchronous messages. We also propose and evaluate different design alternatives for enhancing some VIA functions (such as the VIA Notify mechanism) so that the new substrate can be designed with low overhead. Finally, we derive the best set of alternatives and implement them on two enhanced implementations of VIA (MVIA [3] and Berkeley VIA [24]) on two different networking technologies, Gigabit Ethernet and Myrinet, respectively. We evaluate the performance of our implementation by using several micro-benchmarks and applications. We show that the communication and wait times, and therefore the total execution times of different applications can be significantly reduced by using VIA. A reduction in the overall execution time up to 2.05 on an eight node system is demonstrated in comparison with the original UDP implementation. The new implementation also demonstrates better parallel speedup as the system size increases.

Since a large number of high performance applications are written (and being written) in the distributed memory programming model by using the communication primitives provided by the MPI standard, it is crucial to implement MPI on top of user-level communication protocols. The IBM RS/6000 SP system is one of the most cost-effective commercially available high performance machines. IBM RS/6000 SP systems support the Message Passing Interface standard (MPI) and LAPI [45]. LAPI is a user-level, reliable and efficient one sided communication API library, implemented on IBM RS/6000 SP systems. In Chapter 6, we explain how the high performance of the user-level communication library LAPI has been exploited in order to implement the MPI standard more efficiently than the existing MPI. We describe how to avoid unnecessary data copies at both the sending and receiving sides for such an implementation. The resolution of problems arising from the mismatches between the requirements of the MPI standard and the features of LAPI is discussed. As a result of this exercise, certain enhancements to LAPI are identified to enable an efficient implementation of MPI on LAPI. The performance of the new implementation of MPI is compared with that of the underlying LAPI itself. The latency (in polling and interrupt modes) and bandwidth of our new implementation is compared with that of the native MPI implementation on RS/6000 SP systems. The results indicate that the MPI implementation on LAPI performs comparably or better than the original MPI implementation in most cases. Improvements of up to 17.3% in polling mode latency, 35.8% in interrupt mode latency, and 20.9% in bandwidth are obtained for certain message sizes. It is shown that the implementation of MPI on top of LAPI also outperforms the native MPI implementation for the NAS Parallel Benchmarks.

In Chapter 7, the research contributions of this thesis are summarized. In addition, directions for future research are discussed. Some interesting open problems in related areas are also described.

#### CHAPTER 2

# COMPARISON AND EVALUATION OF DESIGN CHOICES FOR IMPLEMENTING THE VIRTUAL INTERFACE ARCHITECTURE (VIA)

The Virtual Interface Architecture (VIA) [7] is the most important communication protocol developed for clusters. It has been developed to standardize user-level communication protocols. In this chapter, we discuss the essential components of VIA and present different approaches for implementing these components. We discuss the advantages and disadvantages of each approach and present the required support for their implementations. In particular, we discuss different possible approaches for implementing components such as software doorbells, virtual-to-physical address translation, and completion queues. We use the NAS Parallel Benchmarks to study the effect of caching the address translation tables on the NIC and to study different completion queue implementations. We use a subset of VIA implemented on an IBM SP-connected Netfinity cluster [17] running the MS Windows NT operating system and a Myrinet-connected cluster of PCs running the Linux operating system to evaluate different components of VIA.

The rest of this chapter is organized as follows: In Section 2.1, we briefly overview the Virtual Interface Architecture, discuss the VIA send and receive operations in detail, and identify different components involved in these operations. Different design alternatives for implementing these components of VIA are discussed in Section 2.2. The performance evaluation results are presented in Section 2.3. Related work is discussed in Section 2.4. In Section 2.5, we present our conclusions.

# 2.1 Virtual Interface Architecture (VIA)

In this section we first present an overview of VIA. Then, we discuss different events that occur during the send and receive operations and present the basic components involved in performing these operations. We focus on systems with programmable NICs.

#### 2.1.1 Overview

The Virtual Interface Architecture (VIA) is designed to provide high bandwidth, low latency communication support over a System Area Network (SAN). A SAN interconnects the nodes of a distributed computer system[7]. The VIA specification is designed to eliminate the system processing overhead associated with the legacy network protocols by providing user applications a protected and directly accessible network interface called the Virtual Interface (VI).

Each VI is a communication endpoint. Two VI endpoints on different nodes can be logically connected to form a bidirectional point-to-point communication channel. A process can have multiple VIs. A send queue and a receive queue (also called as work queues) are associated with each VI. Applications post send and receive requests to these queues in the form of VIA descriptors. Each

descriptor contains one Control Segment (CS) and zero or more Data Segments (DS) and possibly an Address Segment (AS). Each DS contains a user buffer virtual address. The AS contains a user buffer virtual address at the destination node. Immediate Data mode also exists where the immediate data is contained in the CS. Applications may check the completion status of their VIA descriptors via the *Status* field in CS. A doorbell is associated with each work queue. Whenever an application posts a descriptor, it notifies the VIA provider by ringing the doorbell. Each VI work queue can be associated with a Completion Queue (CQ) too. A CQ merges the completion status of multiple work queues. Therefore, an application need not poll multiple work queues to determine if a request has been completed.

The VIA specification requires that the applications register the virtual memory regions which are going to be used by VIA descriptors and user communication buffers. The intent of the memory registration is to give an opportunity to the VIA provider to pin (lock) down user virtual memory in physical memory so that the network interface can directly access user buffers. This eliminates the need for copying data between user buffers and intermediate kernel buffers typically used in traditional network transports.

The VIA specifies two types of data transfer facilities: the traditional send-receive messaging model and the Remote Direct Memory Access (RDMA) model. In the send/receive model, there is a one to one correspondence between send descriptors on the sending side and receive descriptors on the receiving side. In the RDMA model, the initiator of the data transfer specifies the source and destination virtual addresses on the local and remote nodes, respectively. The RDMA write operation is a required feature of the VIA specification while the RDMA read operation is optional. In this chapter, we focus on the send/receive messaging facilities of VIA.

# 2.1.2 Message Passing in VIA

For sending and receiving messages, the following major steps are taken:

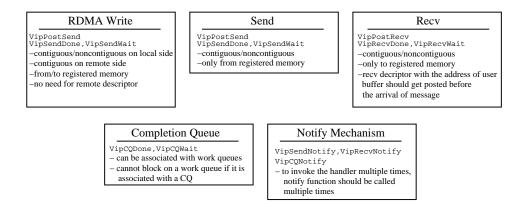

Constructing the descriptor: The application creates a descriptor in a registered memory region. This descriptor includes the virtual address of the send or receive buffer and its length. The message buffer is allocated from a registered memory region. The descriptor also contains a status field which the VIA provider updates upon completion of the operation. Posting the descriptor: The application posts the descriptor using the VipPostSend or VipPostRecv function call. Through the doorbell mechanism, the NIC is informed about the existence of the posted descriptor. Obtaining the descriptor by the NIC: The NIC retrieves from the descriptor the information required for sending or receiving a message. The information includes the address and the length of the user buffer and the address of the status field of the descriptor. **Performing the** operation: The NIC performs the send operation by injecting the data into the network after it is transferred from the user buffer to the NIC. For the receive operation, the message is received from the network into the NIC memory and then into the user buffer. Marking the descriptor as complete: After performing the send or receive operation, the NIC marks the status field of the VIA descriptor as complete. If a CQ is associated with the VI, the NIC also makes an entry in the CQ so that the application can detect the completion through CQ as well. Application detecting the completion of the operation: The application can check the status of the operation using VipSendDone and VipRecvDone in a non-blocking fashion, VipSendWait and VipRecvWait in a blocking fashion, and VipCQDone and VipCQWait if a CQ is associated with the corresponding work queue.

# 2.1.3 Basic Components of VIA

Considering different operations involved in sending and receiving messages, three major components can be identified as the basic components of the message passing operations. These components are: 1) informing the NIC of an outstanding send or receive request, 2) the NIC obtaining information about the outstanding operation and corresponding user data buffers and performing the operation, and 3) the NIC informing the user program of the completion of send and receive operations. In order to implement the send and receive operations efficiently, it is crucial to implement these components as efficiently as possible. In the next section, we present different design alternatives for implementing these components and present the pros and cons of each of them. It should be noted that we only consider the methods which do not require any unnecessary data copies.

### 2.2 Design Alternatives

In this section, we discuss the implementation of doorbells which are related to the first component of message passing operations and are used for informing the NIC of the existence of outstanding send or receive descriptors. We also study different implementations of virtual-to-physical address translation and the possibility of caching descriptors. These two issues relate to the second basic component or the mechanism through which the NIC obtains information about the outstanding operations and corresponding user data buffers. The third component, the mechanism through which the user program is informed of the completion of send and receive operations, is also discussed with respect to the implementation of completion queues.

#### 2.2.1 Doorbells

VIA specifies that each VI be associated with a pair of doorbells. The purpose of a doorbell is to notify the NIC of the existence of newly posted descriptors. Doorbells can be implemented in hardware or software. However, most of the current generation NICs do not provide any hardware support for doorbells, they need to be implemented in software. Therefore, in this chapter, we focus on the design choices for implementing doorbells in software.

Approach 1 (D1): One approach for implementing doorbells in software is allocating space for each doorbell in the NIC memory and mapping it to the address space of the process. The user application rings the doorbell by simply setting the corresponding bit in the NIC memory or by writing the address of the descriptor (or the descriptor itself) in the NIC memory. To protect a doorbell from being tampered by other processes, doorbells of different processes need to be on separate memory pages in the NIC since protection granularity of a kernel is one page (e.g. 4KB). The advantage of using this mechanism is that there is no need to go through the kernel for ringing the doorbells and this operation can be implemented in user space. The disadvantage of this approach is the cost of polling the VIs for send descriptors. As the number of active VIs increases, the NIC spends more time polling the send doorbells to check if there is any send descriptor to be processed. This limits the scalability of the communication subsystem. The other shortcoming of this approach when a single word or bit is used for each VI is that when a descriptor is posted, the subsequent post cannot proceed until the NIC becomes aware of the first posted descriptor. To overcome this shortcoming, a circular buffer can be used as a queue for each VI such that multiple descriptors can be posted by the user application even when the NIC firmware is busy performing

other operations (such as sending and receiving messages) and hasn't become aware of some of the posted descriptors yet.

Approach 2 (D2): In order to avoid the cost of polling of VIs for send descriptors, a second approach in which the kernel intervention is required can be used. In this approach, a centralized queue of send descriptors (or handles to descriptors) are maintained by the NIC. Since all VIs share the same centralized queue, a mechanism is required to guarantee that this queue is accessed in an operating system safe fashion. Thus kernel intervention is required. In this approach, the need for polling all the active VIs is eliminated and the NIC needs to only look at the centralized queue for send descriptors. The disadvantage of this approach is the added delay of going through the kernel. The advantage of this approach is the elimination of the NIC polling active send requests.