# HIGH PERFORMANCE NETWORK I/O IN VIRTUAL MACHINES OVER MODERN INTERCONNECTS

# DISSERTATION

Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University

By

Wei Huang, M.Sc (Tech)

\* \* \* \* \*

The Ohio State University

2008

Dissertation Committee:

Prof. D. K. Panda, Adviser

Prof. P. Sadayappan

Prof. F. Qin

Approved by

Adviser Graduate Program in Computer Science and Engineering © Copyright by

Wei Huang

2008

#### ABSTRACT

With the increasing size and complexity of modern computing systems, a balance between performance and manageability is becoming critical to achieve high performance as well as high productivity computing. Virtual Machine (VM) technology provides various features that help management issues on large-scale computing systems; however, performance concerns have largely blocked the deployment of VMbased computing, especially in the High-Performance Computing (HPC) area.

This dissertation aims at reducing the virtualization overhead and achieving the co-existence of performance and manageability through VM technologies. We focus on I/O virtualization, designing an experimental VM-based computing framework, and addressing performance issues at different levels of the system software stack. We design VMM-bypass I/O, which achieves native I/O performance in VMs by taking advantage of the OS-bypass interconnects. Also with the OS-bypass interconnects, we propose high performance VM migration with Remote Direct Memory Access (RDMA), which drastically reduces the VM management cost. To further improve the communication efficiency on multi-core systems, we design Inter-VM Communication (IVC), a VM-aware communication library to allow efficient shared memory communication among VMs on the same physical host. Finally, we design MVAPICH2-ivc, an MPI library that is aware of VM-based environments and can transparently benefit HPC applications with our proposed designs. The dissertation concludes that performance should no longer be a barrier to deploying VM-based computing, which enhances productivity by achieving much improved manageability with very little sacrifice in performance. Dedicated to my parents, Zhijun and Shiqian;

To my wife, Na

#### ACKNOWLEDGMENTS

I have been lucky to spend my PhD years, which could be the most important five years in my life, with so many great people. While the few words below cannot fully express my gratitude, I write these paragraphs to thank them for their guidance, support and friendliness.

I would like to thank my adviser, Prof. D. K. Panda for his support, patience and guidance throughout the duration of my Ph.D. study. I'm greatly indebted to him for the time and efforts which he spent to lead me into the world of computer science research. I have been learning a lot from his hard work and dedication as an academic researcher.

I am really grateful to Dr. Jiuxing Liu and Dr. Bulent Abali from IBM T. J. Watson Research Center. Topics in this dissertation started as intern projects there and continued at OSU, which would not have been possible without their support and guidance. Especially thanks to Dr. Liu for the pleasant and enlightening discussions over the years.

I would also like to thank my committee members, Prof. P. Sadayappan and Prof. F. Qin for their valuable comments and suggestions.

I'm lucky to have collaborated closely with my colleagues: Matthew, Gopal, Dr. Weikuan Yu, Dr. Hyun-wook Jin, Dr. Karthikeyan Vaidyanathan, Lei, Qi, and Tejus. I would also like to thank them for innumerable discussions and collaborations. I also deeply appreciate the help and support from all my current and past colleagues: Dr. Jiuxing Liu, Dr. Jiesheng Wu, Dr. Pavan Balaji, Dr. Amith Mamidala, Dr. Sayantan Sur, Dr. Abhinav Vishnu, Weihang, Sundeep, Ranjit, Shuang, Ping, Savitha, Hari, Ouyang, KGK, and Jaidev, for their discussions on technical and non-technical issues, as well as their friendship.

Finally, I thank my family: my parents, Zhijun Huang and Shiqian Lou, and my wife, Na Li. My accomplishments are impossible without their love, support, and encouragement throughout the years.

## VITA

| November 25th, 1980          | Born - Hangzhou, China                                                                        |

|------------------------------|-----------------------------------------------------------------------------------------------|

| September 1999 - June 2003   | Bachelor in Computer Science and En-<br>gineering,<br>Zhejiang University,<br>Hangzhou, China |

| September 2003 - August 2004 | University Fellow,<br>The Ohio State University                                               |

| September 2003 - Present     | Graduate Research Associate,<br>The Ohio State University                                     |

| June 2005 - September 2005   | Summer Intern,<br>IBM T. J. Watson Research Center,<br>Hawthorne, NY                          |

| June 2006 - September 2006   | Summer Intern,<br>IBM T. J. Watson Research Center,<br>Hawthorne, NY                          |

| June 2007 - September 2007   | Summer Intern,<br>IBM T. J. Watson Research Center,<br>Hawthorne, NY                          |

## PUBLICATIONS

W. Huang, M. Koop, and D. K. Panda, "Efficient One-Copy MPI Shared Memory Communication in Virtual Machines", In *Proceedings of IEEE Conference on Cluster Computing (Cluster'08)*, Tsukuba, Japan, September, 2008

M. Koop, W. Huang, K. Gopalakrishnan, and D. K. Panda, "Performance Analysis and Evaluation of PCIe 2.0 and Quad-Data Rate InfiniBand", In *Proceedings of the 16th Annual IEEE Symposium on High-Performance Interconnects (Hoti'08)*, Palo Alto, CA, August, 2008

W. Huang, M. Koop, Q. Gao, and D. K. Panda, "Virtual Machine Aware Communication Libraries for High Performance Computing", In *Proceedings of International Conference for High Performance Computing, Networking, Storage and Analysis (SC'07)*, Reno, NV. November, 2007 (*Best Student Paper Finalist*)

W. Huang, Q. Gao, J. Liu, and D. K. Panda, "High Performance Virtual Machine Migration with RDMA over Modern Interconnects", In *Proceedings of IEEE Conference on Cluster Computing (Cluster'07)*, Austin, Texas. September, 2007 (*Selected as a Best Technical Paper*)

K. Vaidyanathan, L. Chai, W. Huang, and D. K. Panda, "Efficient Asynchronous Memory Copy Operations on Multi-Core Systems and I/OAT", In *Proceedings of IEEE Conference on Cluster Computing (Cluster'07)*, Austin, Texas, September, 2007

Q. Gao, W. Huang, M. Koop, and D. K. Panda, "Group-based Coordinated Checkpointing for MPI: A Case Study on InfiniBand", In *Proceedings of Int'l Conference* on *Parallel Processing (ICPP'07)*, XiAn, China, September 2007

W. Huang, J. Liu, M. Koop, B. Abali, and D. K. Panda, "Nomad: Migrating OSbypass Networks in Virtual Machines", In *Proceedings of the 3rd ACM/USENIX Conference on Virtual Execution Environment (VEE'07)*, San Diego, CA. June, 2007

K. Vaidyanathan, W. Huang, L. Chai, and D. K. Panda, "Designing Efficient Asynchronous Memory Operations Using Hardware Copy Engine: A Case Study with I/OAT", In *Proceedings of International Workshop on Communication Architecture for Clusters (CAC)*, held in conjunction with IPDPS '07, March 2007

Q. Gao, W. Yu, W. Huang, and D. K. Panda, "Application-Transparent Checkpoint/Restart for MPI Programs over InfiniBand", In *Proceedings of International Conference on Parallel Processing (ICPP'06)*, Columbus, OH, August, 2006

M. Koop, W. Huang, A. Vishnu, and D. K. Panda, "Memory Scalability Evaluation of the Next-Generation Intel Bensley Platform with InfiniBand", In *Proceedings of the14th IEEE Int'l Symposium on Hot Interconnects (HotI14)*, Palo Alto, CA, August 2006

W. Huang, J. Liu, B. Abali, and D. K. Panda, "A Case of High Performance Computing with Virtual Machines", In *Proceedings of the 20th ACM International Conference* on Supercomputing (ICS'06), Cairns, Queensland, Australia. June, 2006 J. Liu, W. Huang, B. Abali, and D. K. Panda, "High Performance VMM-Bypass I/O in Virtual Machines", In *Proceedings of USENIX Annual Technical Conference 2006* (USENIX'06), Boston, MA. May, 2006

W. Huang, G. Santhanaraman, H. -W. Jin, and D. K. Panda, "Design of High Performance MVAPICH2: MPI-2 over InfiniBand", In *Proceedings of the Sixth IEEE International Symposium on Cluster Computing and the Grid (CCGrid'06)*, Singapore, May, 2006

A. Vishnu, G. Santhanaraman, W. Huang, H. -W. Jin, and D. K. Panda, "Supporting MPI-2 One Sided Communication on Multi-Rail InfiniBand Clusters: Design Challenges and Performance Benefits", In *Proceedings of the International Conference on High Performance Computing (HiPC'05)*, Goa, India, December, 2005

W. Huang, G. Santhanaraman, H. -W. Jin, and D. K. Panda, "Design Alternatives and Performance Trade-offs for Implementing MPI-2 over InfiniBand", In *Proceedings* of *EuroPVM/MPI*, Sorrento, Italy, September 2005

S. Sur, A. Vishnu, H. -W. Jin, W. Huang, and D. K. Panda, "Can Memory-Less Network Adapters Benefit Next-Generation InfiniBand Systems?", In *Proceedings of the 13th Annual IEEE Symposium on High Performance Interconnects (HOTI'05)*, Palo Alto, CA, August, 2005

G. Santhanaraman, J. Wu, W. Huang, D. K. Panda, "Designing Zero-copy MPI Derived Datatype Communication over InfiniBand: Alternative Approaches and Performance Evaluation", The Special Issue of the International Journal of High Performance Computing Applications (IJHPCA) on the Best Papers of EuroPVMMPI 2004

W. Huang, G. Santhanaraman, H. -W. Jin, and D. K. Panda, "Scheduling of MPI-2 One Sided Operations over InfiniBand", In *Proceedings of Workshop on Communication Architecture on Clusters (CAC)* in conjunction with International Parallel and Distributed Processing Symposium (IPDPS), April, 2005

# FIELDS OF STUDY

Major Field: Computer Science and Engineering

Studies in:

| Computer Architecture | Prof. D. K. Panda |

|-----------------------|-------------------|

| Software Systems      | Prof. G. Agrawal  |

| Computer Networks     | Prof. D. Xuan     |

# TABLE OF CONTENTS

## Page

| Abst | ract .                            |                                                     |                                                             | ii                              |

|------|-----------------------------------|-----------------------------------------------------|-------------------------------------------------------------|---------------------------------|

| Dedi | catior                            | 1                                                   |                                                             | iv                              |

| Ackn | owlec                             | lgments                                             |                                                             | v                               |

| Vita |                                   |                                                     |                                                             | vii                             |

| List | of Tal                            | bles                                                |                                                             | xv                              |

| List | of Fig                            | gures .                                             |                                                             | cvi                             |

| Chap | oters:                            |                                                     |                                                             |                                 |

| 1.   | Intro                             | oduction                                            |                                                             | 1                               |

| 2.   | Over                              | view of                                             | Virtualization and High Performance Networking Technologies | 5                               |

|      | <ul><li>2.1</li><li>2.2</li></ul> | 2.1.1<br>2.1.2<br>2.1.3<br>OS-byp<br>2.2.1<br>2.2.2 | OS-bypass I/O                                               | $5 \\ 5 \\ 9 \\ 10 \\ 12 \\ 14$ |

|      | 2.3                               | Messag                                              | e Passing Interface (MPI), MPICH2 and MVAPICH2              | 16                              |

| 3. | Moti         | vation and Problem Statement                                                                                                                                    |

|----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | $3.1 \\ 3.2$ | Benefits of VM-based Computing Environments    19      Performance Limitations of Current I/O Virtualization    21                                              |

|    | 3.3          | Proposed High Performance I/O Virtualization Framework 23                                                                                                       |

| 4. | Low          | Overhead Network I/O in Virtual Machines                                                                                                                        |

|    | 4.1          | VMM-bypass I/O                                                                                                                                                  |

|    | 4.2          | XenIB: Prototype Design and Implementation                                                                                                                      |

|    |              | 4.2.1 Overview                                                                                                                                                  |

|    |              | 4.2.2 InfiniBand Privileged Accesses                                                                                                                            |

|    |              | 4.2.3 VMM-Bypass Accesses                                                                                                                                       |

|    |              | 4.2.4 Virtualizing InfiniBand Management Operations 38                                                                                                          |

|    | 4.3          | XenIB over iWARP/10GibE                                                                                                                                         |

|    | 4.4          | Evaluation of VMM-bypass I/O                                                                                                                                    |

|    |              | 4.4.1 Experimental Setup 40                                                                                                                                     |

|    |              | 4.4.2 InfiniBand Latency and Bandwidth                                                                                                                          |

|    |              | 4.4.3 Event/Interrupt Handling Overhead                                                                                                                         |

|    |              | 4.4.4 Memory Registration                                                                                                                                       |

|    |              | 4.4.5 IPoIB Performance                                                                                                                                         |

|    |              | 4.4.6 MPI Performance $\dots \dots \dots$                       |

|    |              | 4.4.7 iWARP/10GibE Performance                                                                                                                                  |

| 5. | Nom          | ad: Migration of VMM-bypass I/O Networks                                                                                                                        |

|    | 5.1          | Challenges for Migrating VMM-bypass Networks                                                                                                                    |

|    |              | 5.1.1 Location-Dependent Resources                                                                                                                              |

|    |              | 5.1.2 User-Level Communication                                                                                                                                  |

|    |              | 5.1.3 Hardware Managed Connection State Information 54                                                                                                          |

|    | 5.2          | Detailed Design Issues of Nomad                                                                                                                                 |

|    |              | 5.2.1 Location-Dependent Resources                                                                                                                              |

|    |              | 5.2.2 User-Level Communication                                                                                                                                  |

|    |              | 5.2.3 Connection State Information                                                                                                                              |

|    |              | 5.2.4 Unreliable Datagram (UD) Services                                                                                                                         |

|    | 5.3          | Nomad Architecture for XenIB                                                                                                                                    |

|    | 5.4          | Evaluation of Nomad 63                                                                                                                                          |

|    |              | 5.4.1 Experimental Setup $\ldots \ldots \ldots$ |

|    |              | 5.4.2 Micro-benchmark Evaluation                                                                                                                                |

|    |              | 5.4.3 HPC Benchmarks                                                                                                                                            |

|    |              | 5.4.4 Migrating Multiple VMs                                                                                                                                    |

| 6. | Effic | ient Virtual Machine Aware Communication Libraries                                                                                                |

|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

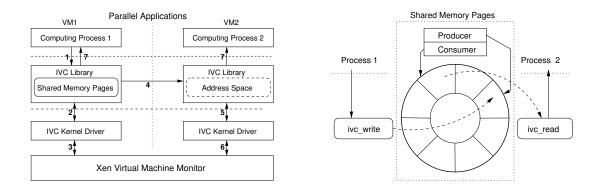

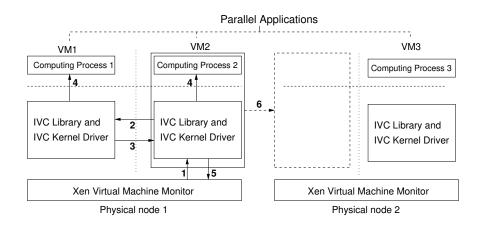

|    | 6.1   | IVC: Efficient Inter-VM Communication through Shared Memory . 71                                                                                  |

|    |       | 6.1.1 Setting up Shared Memory Regions                                                                                                            |

|    |       | 6.1.2 Communication through Shared Memory Regions 73                                                                                              |

|    |       | 6.1.3 Virtual Machine Migration                                                                                                                   |

|    | 6.2   | Virtual Machine Aware MPI-2 Library                                                                                                               |

|    |       | 6.2.1 MVAPICH2: High Performance MPI-2 Library over InfiniBand 78                                                                                 |

|    |       | 6.2.2 MVAPICH2-ivc: Virtual Machine Aware MPI-2 Library 82                                                                                        |

|    | 6.3   | Evaluation of Inter-VM Communication 86                                                                                                           |

|    |       | 6.3.1 Experimental Setup                                                                                                                          |

|    |       | 6.3.2 Micro-benchmark Evaluation                                                                                                                  |

|    |       | 6.3.3 Application-level Benchmark Evaluation                                                                                                      |

| 7. | Effic | ient One-copy Shared Memory Communication                                                                                                         |

|    | 7.1   | Motivation                                                                                                                                        |

|    | 7.2   | One-copy Protocol for Inter-VM Shared Memory Communication . 99                                                                                   |

|    | 7.3   | IGMC: Inter-VM Grant/Mapping Cache                                                                                                                |

|    |       | 7.3.1 Evicting Cache Entries $\dots \dots \dots$  |

|    |       | 7.3.2 Improving the Cache Hit Ratio                                                                                                               |

|    |       | 7.3.3 Fall-back Mechanism $\ldots \ldots 10'$          |

|    | 7.4   | Evaluation $\ldots \ldots \ldots$ |

|    |       | 7.4.1 Experimental Setup                                                                                                                          |

|    |       | 7.4.2 Micro-benchmarks Evaluation                                                                                                                 |

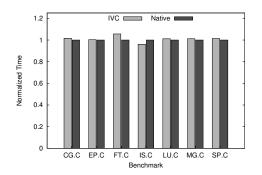

|    |       | 7.4.3 NAS Parallel Benchmarks                                                                                                                     |

| 8. | High  | Performance Virtual Machine Migration over RDMA 118                                                                                               |

|    | 8.1   | Potential Benefits of RDMA based Migration                                                                                                        |

|    | 8.2   | Design Challenges                                                                                                                                 |

|    | 8.3   | Detailed Design Issues and Solutions                                                                                                              |

|    |       | 8.3.1 RDMA based Migration Protocols                                                                                                              |

|    |       | 8.3.2 Memory Registration                                                                                                                         |

|    |       | 8.3.3 Page Clustering                                                                                                                             |

|    |       | 8.3.4 Network Quality of Service                                                                                                                  |

|    | 8.4   | Evaluation of RDMA-based Virtual Machine Migration                                                                                                |

|    |       | 8.4.1 Experimental Setup                                                                                                                          |

|    |       | 8.4.2 Basic Migration Performance                                                                                                                 |

|    |       | 8.4.3 Impact of Migration on Hosted Applications                                                                                                  |

|    |       | 8.4.4 Impact of Migration on Parallel Applications                                                                                                |

|      | 8.4.5 Impact of Adaptive Limit Control on Network QoS                | 133 |

|------|----------------------------------------------------------------------|-----|

| 9.   | Open Source Software Release and Its Impact                          | 135 |

| 10.  | Conclusion and Future Research Directions                            | 137 |

|      | 10.1 Summary of Research Contributions                               | 137 |

|      | 10.1.1 VMM-bypass I/O to Remove Performance Bottleneck in VMs        | 138 |

|      | 10.1.2 Migration of OS-bypass Networks                               | 139 |

|      | 10.1.3 Inter-VM Shared Memory Communication                          | 140 |

|      | 10.1.4~ Evaluation with Micro-benchmarks and Real Applications $~$ . | 141 |

|      | 10.1.5 VM Migration with RDMA                                        | 142 |

|      | 10.2 Future Research Directions                                      | 142 |

| Bibl | iography                                                             | 146 |

# LIST OF TABLES

| Table |                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1   | Distribution of execution time for NAS                                                                                                     |

| 4.1   | Distribution of execution time for NAS                                                                                                     |

| 5.1   | NAS Communication patterns: number of total messages to the most frequently communicated peer and the average message size to that peer 67 |

| 7.1   | Communication pattern of NPB (Class A) 112                                                                                                 |

| 8.1   | Sample instruction count, L2 cache misses and TLB misses (collected using Xenoprof [33]) 132                                               |

# LIST OF FIGURES

| Fig | Figure                                                                                 |  | ge |

|-----|----------------------------------------------------------------------------------------|--|----|

| 2.1 | The Xen architecture (courtesy [48])                                                   |  | 6  |

| 2.2 | OS-Bypass Communication and I/O                                                        |  | 11 |

| 2.3 | InfiniBand Architecture (Courtesy InfiniBand Specifications)                           |  | 13 |

| 2.4 | Architectural overview of OpenFabrics driver stack $\ldots \ldots \ldots$              |  | 14 |

| 2.5 | Compare iWARP with traditional TCP/IP layers (Courtesy $\left[ 11 \right] \right) ~~.$ |  | 15 |

| 2.6 | Layered design of MPICH2                                                               |  | 17 |

| 3.1 | A possible deployment of HPC with virtual machines $\ldots \ldots \ldots$              |  | 20 |

| 3.2 | NAS Parallel Benchmarks                                                                |  | 21 |

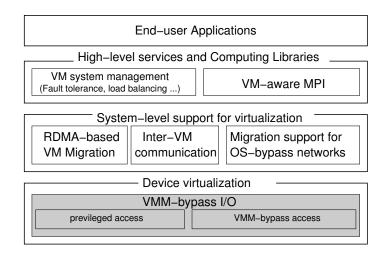

| 3.3 | Proposed research framework                                                            |  | 24 |

| 4.1 | Network I/O in proposed research framework                                             |  | 29 |

| 4.2 | VMM-bypass (I/O Handled by VMM Directly)                                               |  | 31 |

| 4.3 | VMM-bypass (I/O Handled by Another VM)                                                 |  | 31 |

| 4.4 | The Xen-IB driver structure with the split driver model                                |  | 33 |

| 4.5 | VMM-Bypass design of Xen-IB driver                                                     |  | 37 |

| 4.6 | Working flow of the VMM-bypass Xen-IB driver                                           |  | 37 |

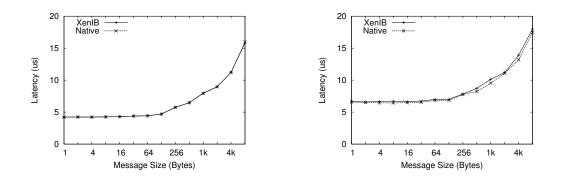

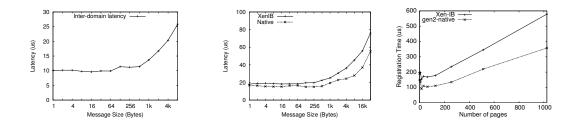

| 4.7  | InfiniBand RDMA write latency                       | 42 |

|------|-----------------------------------------------------|----|

| 4.8  | InfiniBand send/receive latency                     | 42 |

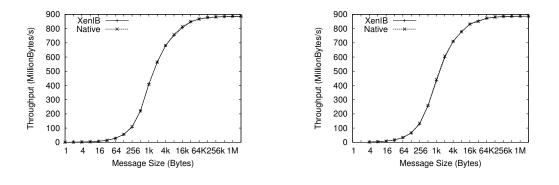

| 4.9  | InfiniBand RDMA write bandwidth                     | 42 |

| 4.10 | InfiniBand send/receive bandwidth                   | 42 |

| 4.11 | Inter-domain Communication One Way Latency          | 43 |

| 4.12 | Send/Receive Latency Using Blocking VERBS Functions | 43 |

| 4.13 | Memory Registration Time                            | 43 |

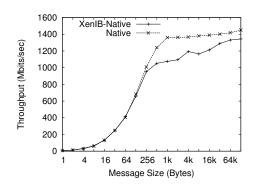

| 4.14 | IPoIB Netperf Throughput                            | 46 |

| 4.15 | Netperf Transaction Test                            | 46 |

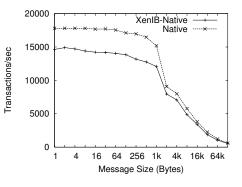

| 4.16 | MPI latency test                                    | 47 |

| 4.17 | MPI bandwidth test                                  | 47 |

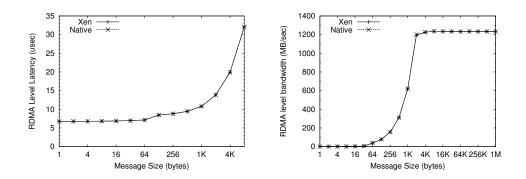

| 4.18 | NAS Parallel Benchmarks (16 processes, class B)     | 48 |

| 4.19 | HPL on 2, 4, 8 and 16 processes                     | 48 |

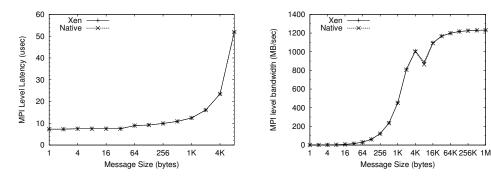

| 4.20 | RDMA level latency test                             | 49 |

| 4.21 | RDMA level bandwidth test                           | 49 |

| 4.22 | MPI level latency test                              | 50 |

| 4.23 | MPI level bandwidth test                            | 50 |

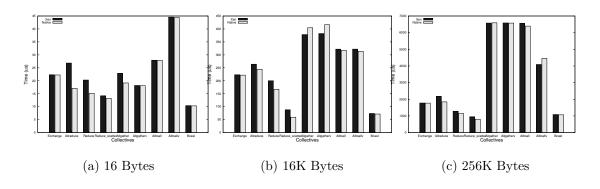

| 4.24 | MPI collective operations                           | 51 |

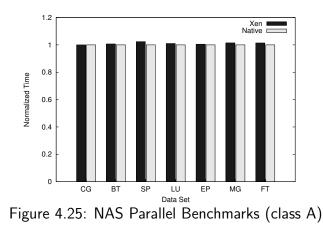

| 4.25 | NAS Parallel Benchmarks (class A)                   | 51 |

| 5.1  | Network I/O in proposed research framework          | 53 |

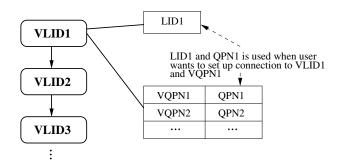

| 5.2  | Destination mapping table                           | 57 |

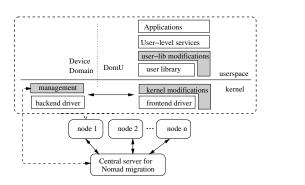

| 5.3  | Architecture of Nomad                                                      | 61 |

|------|----------------------------------------------------------------------------|----|

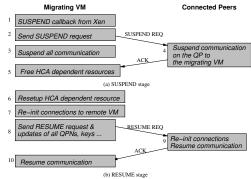

| 5.4  | Protocol for migrating one VM                                              | 61 |

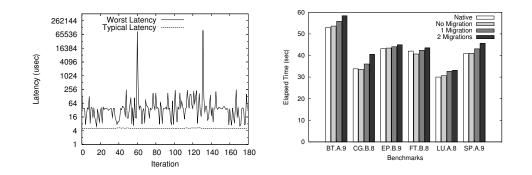

| 5.5  | Impact of migration on RDMA latency                                        | 65 |

| 5.6  | Impact of migration on NAS benchmarks (migrating one VM out of eight)      | 65 |

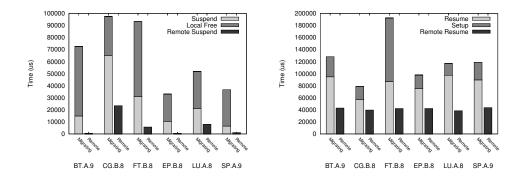

| 5.7  | Suspend time running NAS benchmarks                                        | 68 |

| 5.8  | Resume time running NAS benchmarks                                         | 68 |

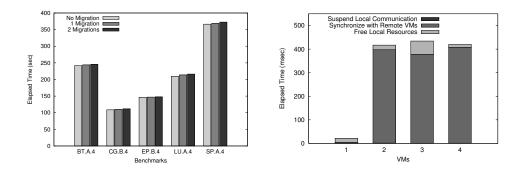

| 5.9  | Impact of migration on NAS benchmarks (migrating all four VMs)             | 70 |

| 5.10 | Suspend time running NAS-CG                                                | 70 |

| 6.1  | VM-aware communication libraries in the proposed research framework        | 72 |

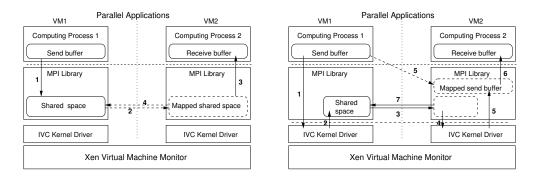

| 6.2  | Mapping shared memory pages                                                | 74 |

| 6.3  | Communication through mapped shared memory regions $\ldots$                | 74 |

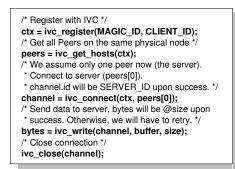

| 6.4  | A very brief client-server example for using IVC                           | 75 |

| 6.5  | Migrating one VM (VM2) of a three-process parallel job hosted on three VMs | 77 |

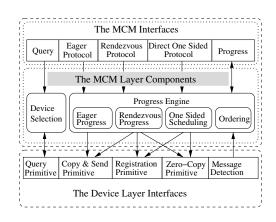

| 6.6  | Overall design of MVAPICH2                                                 | 79 |

| 6.7  | Design details of the MCM layer                                            | 79 |

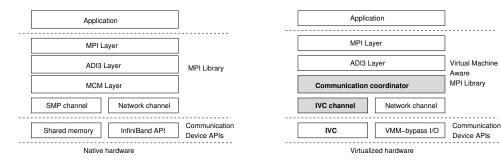

| 6.8  | MVAPICH2 running in native environment                                     | 83 |

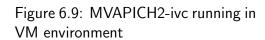

| 6.9  | MVAPICH2-ivc running in VM environment                                     | 83 |

| 6.10 | Organization of IVC-active list in MVAPICH2-ivc                            | 85 |

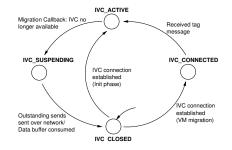

| 6.11 | State transition graph of <i>ivc state</i>                                 | 85 |

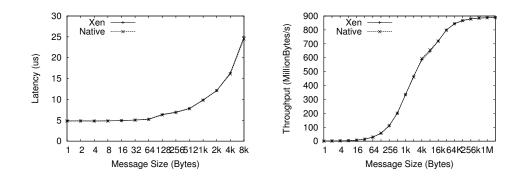

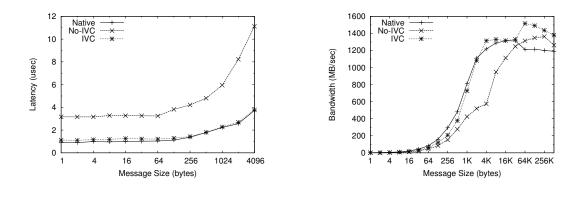

| 6.12 | Latency                                                                  | 89  |

|------|--------------------------------------------------------------------------|-----|

| 6.13 | Bandwidth                                                                | 89  |

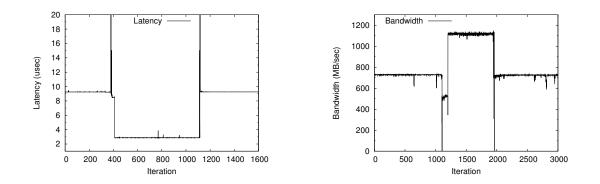

| 6.14 | Migration during latency test                                            | 90  |

| 6.15 | Migration during bandwidth test                                          | 90  |

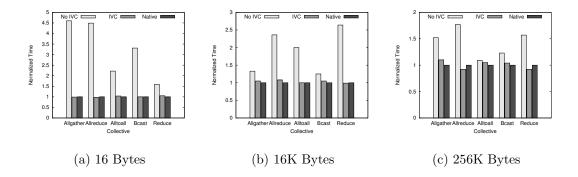

| 6.16 | Comparison of collective operations (2 nodes with 8 cores each) $\ldots$ | 91  |

| 6.17 | Application-level evaluation on Testbed B (2 nodes with 8 cores each)    | 93  |

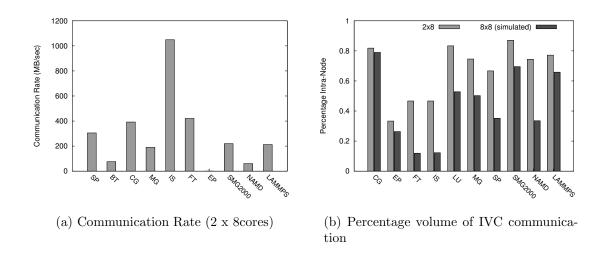

| 6.18 | Communication patterns of the evaluated applications                     | 94  |

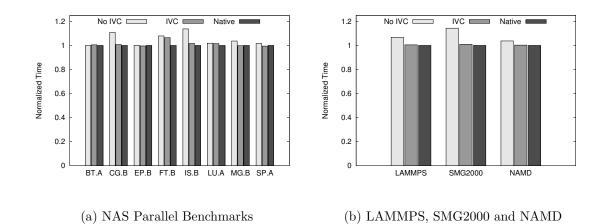

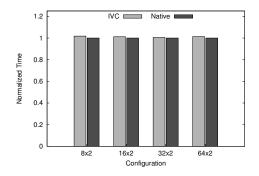

| 6.19 | Normalized Execution time of NAS (64 nodes with 2 processors each)       | 96  |

| 6.20 | Normalized Execution time of HPL                                         | 96  |

| 7.1  | Protocols to send MPI messages                                           | 100 |

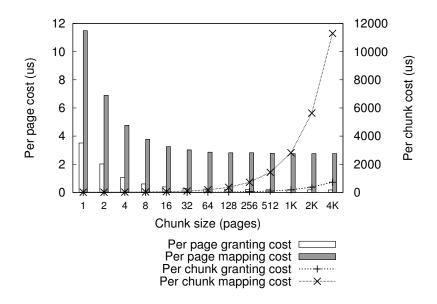

| 7.2  | Cost of granting/mapping pages                                           | 101 |

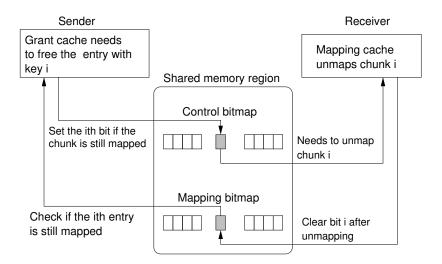

| 7.3  | Exchanging control information through bitmaps                           | 106 |

| 7.4  | MPI latency                                                              | 110 |

| 7.5  | MPI bandwidth                                                            | 110 |

| 7.6  | MPI latency with cyclic access pattern                                   | 110 |

| 7.7  | MPI bandwidth with cyclic access pattern                                 | 110 |

| 7.8  | MPI latency (mapping cache miss)                                         | 111 |

| 7.9  | MPI bandwidth (mapping cache miss)                                       | 111 |

| 7.10 | Relative performance for NPB                                             | 113 |

| 7.11 | Percentage of intra-node communication for larger scale run with NPB     | 113 |

| 8.1  | High performance VM migration in proposed research framework             | 115 |

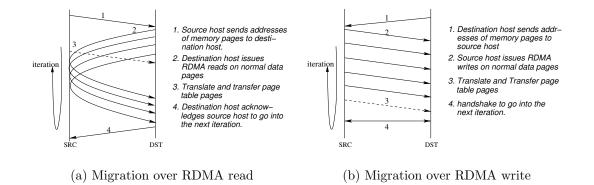

| 8.2  | Migration over RDMA                                            | 119 |

|------|----------------------------------------------------------------|-----|

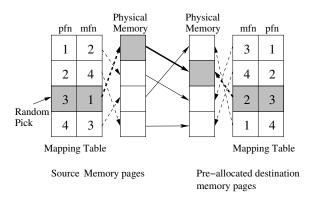

| 8.3  | Memory page management for a "tiny" OS with four pages         | 122 |

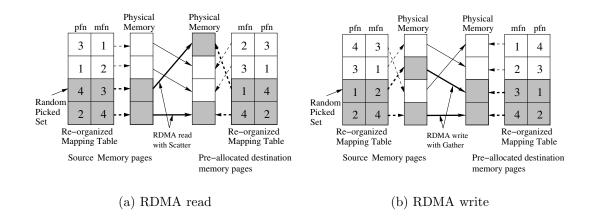

| 8.4  | Re-organizing mapping tables for page clustering               | 123 |

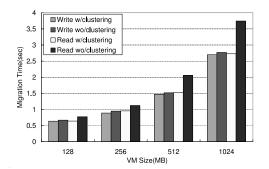

| 8.5  | Benefits of page-clustering                                    | 127 |

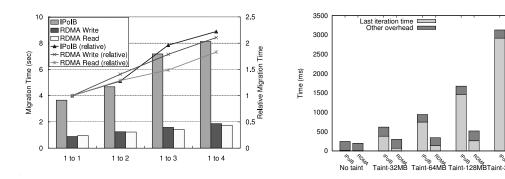

| 8.6  | Total migration time                                           | 127 |

| 8.7  | "Root-to-all" migration                                        | 129 |

| 8.8  | Migration downtime                                             | 129 |

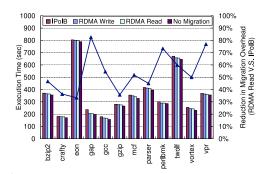

| 8.9  | SPEC CINT 2000 (2 CPUs)                                        | 130 |

| 8.10 | SPEC CINT 2000 (1 CPU)                                         | 130 |

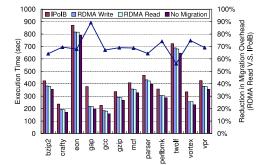

| 8.11 | Impact of migration on applications in a non-migrating VM $\ $ | 131 |

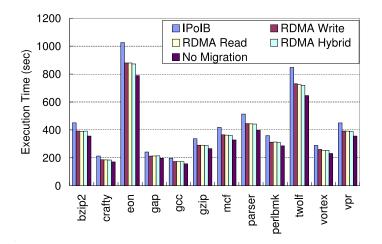

| 8.12 | Impact of migration on NAS Parallel Benchmarks                 | 133 |

| 8.13 | Adaptive rate limit control                                    | 134 |

#### CHAPTER 1

#### **INTRODUCTION**

With ever-increasing computing power being demanded by modern applications, today's ultra-scale data centers and High Performance Computing (HPC) systems are being deployed with increasing size and complexity. These large scale systems require significant system management effort, including maintenance, reconfiguration, fault tolerance, and administration, which are not necessarily the concerns of earlier small scale systems. As a result, system manageability is widely considered a critical requirement for modern computing environments.

Recent Virtual Machine (VM) technology emphasizes ease of system management and administration. Through a Virtual Machine Monitor (VMM or hypervisor), which is implemented directly on hardware, this technology allows running multiple guest VMs on a single physical node, with each guest VM possibly running a different Operating System (OS) instance. VM technology separates hardware and software management and provides useful features including performance isolation, server consolidation and live migration [10]. VMs provide secure and portable environments to meet the demanding resource requirements of modern computing systems and have been widely adopted in industry computing environments, especially data centers. The benefits of VMs are at the penalty of performance degradation, however, by adding a virtualization layer between the OS instances and the native hardware resources. To reduce performance overhead, modern VMMs such as Xen [12] and VMware [67] allow guest VMs to access hardware resources directly whenever possible. For example, a guest VM can execute all non-privileged instructions natively in hardware without intervention of the VMM. Since many CPU intensive workloads seldom use privileged operations, the CPU virtualization overhead can be extremely low. Unfortunately, such direct access optimizations are not always possible. I/O virtualization is an example. Because I/O devices are usually shared among all VMs in a physical machine, the VMM has to make sure that accesses to them are valid and consistent. Currently, this requires VMM intervention on every I/O access from guest VMs, which leads to longer I/O latency and higher CPU overhead due to the context switches between the guest VMs and the VMM. In some cases, this I/O virtualization overhead weighs heavily against the wider adoption of VM technology, especially in the area of High Performance Computing (HPC).

Modern computing systems, featured with multi-core architecture and high performance networks, bring both opportunities and challenges to VM technology. On one side, the intelligent modern high speed interconnects connecting parallel systems, such as InfiniBand [21], typically allow OS-bypass [5, 44, 49, 61, 62] accesses. OS-bypass carries time-critical operations directly from user space applications to hardware while still maintaining system integrity and isolation. Based on OS-bypass, we can design VMM-bypass I/O virtualization, removing the bottleneck of going through the VMM or a separate VM for many I/O operations, and significantly improving communication and I/O performance. This potentially eliminates the performance barrier that prevents performance-critical applications from taking advantage of various features available through VM technology. On the other hand, OS-bypass networks pose additional challenges to VM migration because not all I/O operations can be intercepted by the VMM. Multi-core architecture also increases the level of server consolidation, requiring much more efficient inter-VM communication.

This dissertation aims at designing an efficient I/O virtualization framework for current and next-generation computing systems with high speed interconnects and multi-core architecture. We mainly target HPC environments, where VM deployments are severely limited because of the performance concerns while the features of VMs are welcomed to help the management issues on increasingly larger systems. We focus on network I/O operations, and propose a high performance VMM-bypass I/O virtualization technique that achieves native-level performance in VM-based environments. We design efficient middleware to benefit applications and VM management through our proposed techniques. More specifically, we have addressed the following questions:

- How can we reduce the network I/O virtualization overhead in modern computing systems featuring high speed interconnects and multi-core architecture?

- How can we reduce the cost of inter-VM communication on the same physical host, which is especially important for multi-core architecture?

- How can we design efficient middleware so that applications running in VMbased environments can benefit transparently from our research?

- How can we further reduce the management overhead for VM-based computing environments by taking advantage of modern high speed interconnects?

The rest of this dissertation is organized as follows. In Chapter 2, we discuss the existing technologies which provide background information of our work, including VM technology, InfiniBand architecture and MPI. In Chapter 3, we define the problems that we are addressing in this dissertation. Chapters 4 - 8 discuss our detailed approaches and results. We introduce the open source software packages derived from our work in Chapter 9. Finally in Chapter 10, we conclude and discuss some future research directions.

#### CHAPTER 2

# OVERVIEW OF VIRTUALIZATION AND HIGH PERFORMANCE NETWORKING TECHNOLOGIES

In this chapter, we discuss several important technologies that are related to our research, including VMs, OS-bypass I/O, InfiniBand and iWARP/10GibE architecture, and Message Passing Interface (MPI). This will provide appropriate background information for this dissertation.

#### 2.1 Virtual Machines

First we introduce VM technology using Xen as an example. Xen [12] is a popular high performance virtual machine monitor originally developed at the University of Cambridge. We start with a brief overview of the Xen architecture. We then describe how I/O is virtualized through the Xen split device driver model. Finally we discuss how Xen performs VM migration.

#### 2.1.1 Xen Architecture

Xen adopts para-virtualization [70], in which host operating systems need to be explicitly ported to the Xen architecture. This architecture is similar to native hardware such as x86 architecture, with only slight modifications to support efficient virtualization. Since Xen does not require changes to the application binary interface (ABI), existing applications can run without any modifications.

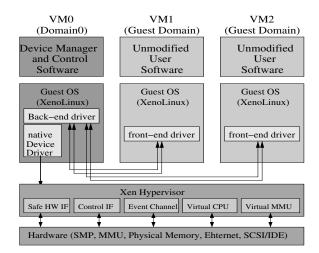

Figure 2.1: The Xen architecture (courtesy [48])

Figure 2.1 illustrates a physical machine running the Xen hypervisor. The Xen hypervisor is at the lowest level and has direct access to the hardware. Xen needs to ensure that the hypervisor, instead of the guest operating systems, is running in the most privileged processor-level. The x86 privilege levels are described by "rings", from ring 0 (the most privileged) to ring 3 (the least privileged). The hypervisor is running in ring 0. It provides basic control interfaces needed to perform complex policy decisions in Xen architecture. Above the hypervisor are the Xen domains (VMs). There can be many domains running simultaneously. Each domain hosts a guest operating system. Instead of running in ring 0, Guest OSes are modified to run in ring 1, which prevents them from directly executing the privileged processor instructions. Guest applications, like on normal x86 machines, run in ring 3 (the least

privileged level). Only domain0 (dom0), which is created at boot time, is allowed to access the control interface provided by the hypervisor. The guest OS on dom0 hosts the application-level management software and performs the tasks to create, terminate or migrate other domains through the control interface provided by the hypervisor.

There is no guarantee that a domain will get a continuous stretch of physical memory to run a guest OS. So Xen makes a distinction between *machine memory* and pseudo-physical memory. Machine memory refers to the physical memory installed in the machine. On the other hand, pseudo-physical memory is a per-domain abstraction, allowing a guest OS to treat its memory as consisting of a contiguous range of physical pages. Xen maintains the mapping between the machine memory (machine frame number or mfn) and the pseudo physical memory (physical frame number or pfn). Only certain specialized parts of the operating system need to understand the difference between these two abstractions. Guest OSes allocate and manage their own hardware page tables, with minimal involvement of the Xen hypervisor to ensure safety and isolation. To achieve efficient memory accesses in each domain, guest OSes allocate and manage their own hardware page tables. A read from a page table does not need to involve the Xen hypervisor, and thus introduces no overhead. However, all updates to the page tables must be verified by Xen to ensure safety and isolation. There are several restrictions for updating the page tables: a guest OS may only map pages that it owns, and page-table pages may only be mapped as read only, etc.

In Xen, domains communicate with each other through *event channels*. Event channels provide an asynchronous notification mechanism between Xen domains. Each domain has a set of end-points (or ports) which may be bounded to an event source (e.g. a physical Interrupt Request (IRQ), a virtual IRQ, or a port in another domain) [58]. When a pair of end-points in two different domains are bound together, a "send" operation on one side will cause an event to be received by the destination domain. Event channels are only intended for sending notifications between domains. So if one domain wants to send data to another one, the typical scheme is for a source domain to grant access to local memory pages to the destination domain. Then, these shared pages are used to transfer data.

#### 2.1.2 Xen Device Access Models

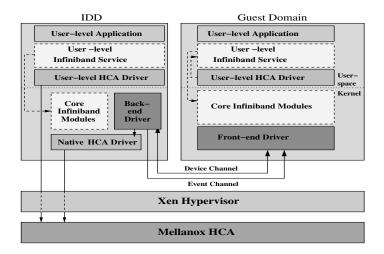

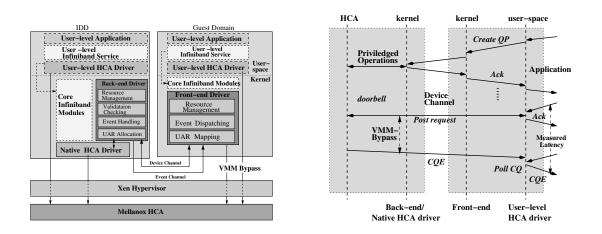

VMs in Xen usually do not have direct access to hardware. Because most existing device drivers assume they have complete control of the device, there cannot be multiple instantiations of such drivers in different domains for a single device. To ensure manageability and safe access, device virtualization in Xen follows a split device driver model [14]. Each device driver is expected to run in an *isolated device domain (IDD)*, which also hosts a *back-end* driver, running as a daemon and serving the access requests from guest domains. Each guest OS uses a *front-end* driver to communicate with the back-end. The front-end and back-end drivers communicate through the shared memory page and the event channel mechanism described above. This split driver organization provides security: misbehaving code in a guest domain will not result in failures of other guest domains. To improve the throughput for devices that need large data transfer such as network I/O, only the request descriptors can be passed to the IDD. The actual data payload may be directly DMAed (Direct Memory Access) from the guest domain to the device.

model requires the development of front-end and back-end drivers for each individual device, not all devices are supported in guest domains right now.

#### 2.1.3 Virtual Machine Migration

Migration is one of the most important features provided by modern VM technology. It allows system administrators to move an OS instance to another physical node without interrupting any hosted services on the migrating OS. It is an extremely powerful cluster administration tool and serves as a basis for many modern administration frameworks which aim to provide efficient online system maintenance, reconfiguration, load balancing and proactive fault tolerance in clusters and data centers [7, 38, 55, 74]. In such management frameworks, it is desirable that VM migration be carried out in a very efficient manner, with both short migration times and low impacts on hosted applications.

When migrating a guest  $OS^1$ , Xen first enters the *pre-copy* stage, where all the memory pages used by the guest OS are transferred from the source to pre-allocated memory regions on the destination host. This is done by user level *migration helper processes* in Dom0s of both hosts. All memory pages of the migrating OS instance (VM) are mapped to the address space of the *helper processes*. After that the memory pages are sent to the destination host over TCP/IP sockets. Memory pages containing page tables need special attention that all machine dependent addresses (*mfn*) are translated to machine independent addresses (*pfn*) before the pages are sent. The addresses will be translated back to *mfn* at the destination host. This ensures transparency since guest OSes reference memory by *pfn*. Once all memory pages are

<sup>&</sup>lt;sup>1</sup>For Xen, each domain (VM) hosts only one operating system. Thus, we do not distinguish among migrating a VM, a domain, and an OS instance in this dissertation.

transferred, the guest VM on the source machine is discarded, and the execution will resume on the destination host.

Xen also adopts live migration [10], where the pre-copy stage involves multiple iterations. The first iteration sends all the memory pages, and the subsequent iterations copy only those pages dirtied during the previous transfer phase. The pre-copy stage terminates when the page dirty rate exceeds the page transfer rate or when the number of iterations exceeds a pre-defined value. One of the benefits of live migration is that the guest OS is still active during the *pre-copy* stage, thus the actual *downtime* will be short. The only observed downtime is at the last iteration of pre-copy, when the VM is shut down to prevent any further modification to the memory pages.

### 2.2 OS-bypass I/O and InfiniBand Architecture

In this section we describe OS-bypass networks, InfiniBand, and iWARP/10GibE architecture.

#### 2.2.1 OS-bypass I/O

Traditionally, device I/O accesses are carried out inside the OS kernel on behalf of application processes. However, this approach imposes several problems such as overhead caused by context switches between user processes and OS kernels and extra data copies which degrade I/O performance [4]. It can also result in *QoS crosstalk* [17] due to lacking of proper accounting for costs of I/O accesses carried out by the kernel on behalf of applications.

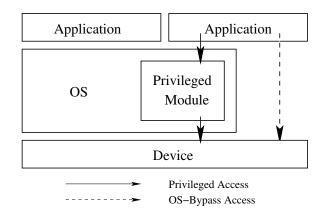

To address these problems, a concept called user-level communication was introduced by the research community. One of the notable features of user-level communication is *OS-bypass*, with which I/O (communication) operations can be achieved directly by user processes without involving OS kernels. OS-bypass was later adopted by commercial products, many of which have become popular in areas such as high performance computing where low latency is vital to applications. It should be noted that OS-bypass does not mean all I/O operations bypass the OS kernel. Usually, devices allow OS-bypass for frequent and time-critical operations while other operations, such as setup and management operations, can go through OS kernels and are handled by a privileged module, as illustrated in Figure 2.2.

Figure 2.2: OS-Bypass Communication and I/O

The key challenge in implementing OS-bypass I/O is to enable safe access to a device shared by many different applications. To achieve this, OS-bypass capable devices usually require more intelligence in the hardware than traditional I/O devices. Typically, an OS-bypass capable device is able to present virtual access points to different user applications. Hardware data structures for virtual access points can be encapsulated into different I/O pages. With the help of an OS kernel, the I/O pages can be mapped into the virtual address spaces of different user processes. Thus, different processes can access their own virtual access points safely, thanks to the protection provided by the virtual memory mechanism. Although the idea of userlevel communication and OS-bypass was developed for traditional, non-virtualized systems, the intelligence and self-virtualizing characteristic of OS-bypass devices land themselves nicely to a virtualized environment, as we will see later.

#### 2.2.2 InfiniBand

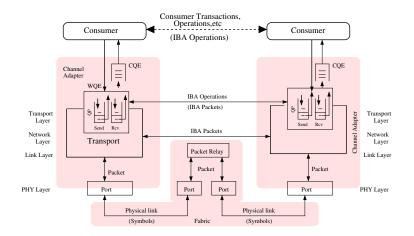

InfiniBand [21] is a typical OS-bypass interconnect offering high performance. Figure 2.3 illustrates the InfiniBand architecture. The InfiniBand communication stack consists of many layers. The interface presented by Channel adapters to consumers belongs to the transport layer. A queue-based model is used in this interface. A *Queue Pair (QP)* in InfiniBand Architecture consists of a send queue and a receive queue. The send queue holds instructions to transmit data and the receive queue holds instructions that describe where received data is to be placed. Communication instructions are described in *Work Queue Requests (WQR)*, or descriptors, and are submitted to the work queue. Once submitted, a WQR becomes a *Work Queue Element (WQE)*, and are executed by Channel Adapters. The completion of WQEs is reported through *Completion Queues (CQs)*. Once a WQE is finished, a *Completion Queue Entry (CQE)* is placed in the associated CQ. A kernel application can subscribe for notifications from InfiniBand Network Interface Card (NIC, or Host Channel Adapter, HCA) and register a callback handler with a CQ. A CQ can also be accessed through polling to reduce latency.

Initiating data transfer (posting work requests) and completion of work requests notification (poll for completion) are time-critical tasks that need to be performed by

Figure 2.3: InfiniBand Architecture (Courtesy InfiniBand Specifications)

the application. In the Mellanox [30] approach, which represents a typical implementation of InfiniBand specification, these operations are done by ringing a doorbell. Doorbells are rung by writing to the registers that form the *User Access Region* (*UAR*). UAR is memory-mapped directly from a physical address space that is provided by Host Channel Adapter (HCA). It allows access to HCA resources from privileged as well as unprivileged mode. Each UAR is a 4k page. Mellanox HCAs replicate the UARs up to 16M times. Each process using the HCA, whether in kernel space or user space, is allocated one UAR, which is remapped to the process's virtual address space. Posting a work request includes putting the descriptors (WQR) in QP buffer and writing the doorbell to the UAR. This process can be completed without the involvement of the operating system, so it is very fast. CQ buffers, where the CQEs are located, can also be directly accessed from the process virtual address space. These OS-bypass features make it possible for InfiniBand to provide very low communication latency. Mellanox HCAs require all buffers involved in communication be registered before they can be used in data transfers. The purpose of registration is two-fold: first an HCA needs to keep an entry in the Translation and Protection Table (TPT) so that it can perform virtual-to-physical translation and protection checks during data transfer; second the memory buffer needs to be pinned in memory so that HCA can DMA directly into the target buffer. Upon the success of registration, a local key and a remote key are returned. They will be used later for local and remote (RDMA) accesses. The QP and CQ buffers described above are just normal buffers that are directly allocated from process virtual memory space and registered with HCA.

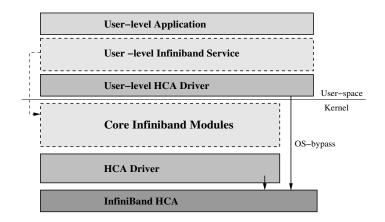

Figure 2.4: Architectural overview of OpenFabrics driver stack

OpenFabrics [42] is the most popularly used InfiniBand driver stack currently. Figure 2.4 presents its architecture.

#### 2.2.3 iWARP/10GibE

iWARP stands for Internet Wide Area RDMA Protocol. It defines Remote Direct Memory Access (RDMA) operations over Ethernet networks [51]. Basically, iWARP allows for zero-copy data transfer over the legacy TCP/IP communication stacks. It bringing the benefits of OS-bypass to the Internet community, including significantly higher communication performance and low CPU overhead. Applications use the verbs API which provides RDMA support instead of traditional Socket API. As specified in [51], the basic message transport for iWARP is undertaken by the TCP layer. Since TCP itself is a stream protocol and does not respect message boundaries, an additional MPA layer is introduced to enforce this, as illustrated in Figure 2.5. The actual zero-copy capability is enabled by the Direct Data Placement (DDP) Layer. The RDMA features provided by DDP are exported to the upper level protocol by the RDMAP layer. Though iWARP can be implemented with either software [11] or hardware, it is intended to be implemented in hardware to achieve a significant performance improvement over the traditional TCP/IP stacks.

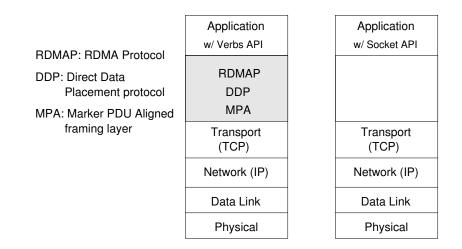

Figure 2.5: Compare iWARP with traditional TCP/IP layers (Courtesy [11])

The Chelsio [9] 10GibE adapter supports a hardware implementation of iWARP protocol. It supports both a private programming interface as well as the aforementioned OpenFabrics interface. We focus on the OpenFabrics interface in our research. From the iWARP perspective, the exposed software interface by OpenFabrics stack (verbs) to interact with hardware is very similar to the interface for Mellanox HCA, except for different layouts in the UARs or QP/CQ buffers etc. Thus, we will not provide additional details here.

## 2.3 Message Passing Interface (MPI), MPICH2 and MVA-PICH2

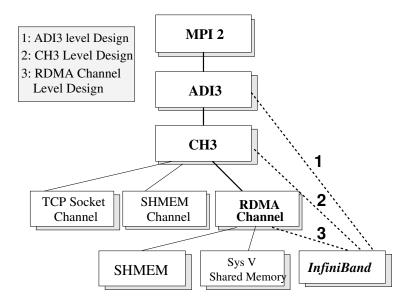

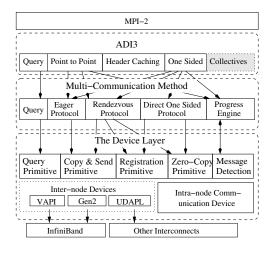

MPI is currently the de facto standard for parallel programming. MPI-2 is the latest MPI standard and supports both point to point and one sided operations which are also referred to as Remote Memory Access (RMA) operations. MPICH2 is a portable implementation of MPI-2 from Argonne National Lab[2]. Figure 2.6 describes the layered approach provided by MPICH2 for designing MPI-2 over RDMA capable networks like InfiniBand.

Implementation of MPICH2 on InfiniBand can be done at one of the three layers in the current MPICH2 stack: RDMA channel, CH3 and ADI3. The decision is usually based on the trade-offs between communication performance and ease of porting.

RDMA channel is at the lowest position in the hierarchical structure of MPICH2. All the communication operations that MPICH2 supports are mapped to just five functions at this layer. In the five-function-interface only two (*put* and *read*) are communication functions, thus providing the least porting overhead. The interface needs to conform to stream semantics, which deliver data in FIFO order, and inform the upper layer of the number of bytes successfully sent. It is especially designed for

Figure 2.6: Layered design of MPICH2

architectures with RDMA capabilities, which directly fit with InfiniBand's RDMA semantics.

The CH3 layer provides a *channel* device that consists of a dozen functions. It accepts the communication requests from the upper layer and informs the upper layer once the communication has completed. The CH3 layer is responsible for making communication progress, which is the added complexity associated with implementing MPI-2 at this layer. But meanwhile, it can also access more performance oriented features than the RDMA channel layer. Thus, at this layer, we have more flexibility to optimize the performance.

The ADI3 is a full-featured, abstract device interface used in MPICH2. It is the highest layer in MPICH2 hierarchy. A large number of functions must be implemented to bring out a ADI3 design, but it can also provide flexibility for many optimizations, which are hidden from lower layers. MVAPICH2 is a high performance implementation of MPI-2 over InfiniBand[69] from the Network Based Computing Laboratory at the Ohio State University. This software was originally designed based on the RDMA channel in MPICH2 [36], which is reflected in an earlier public released version MVAPICH2-0.6.5. In that design, we use eager and rendezvous schemes to support the communication interfaces of the RDMA channel. For small messages, we use the eager protocol. It copies messages to pre-registered buffers and sends them through RDMA write operations, which achieves good latency. And for large messages, a zero-copy rendezvous protocol is used, because using pre-registered buffers introduces high copy overhead. The user buffer is registered on the fly and sent directly through RDMA.

## CHAPTER 3

## MOTIVATION AND PROBLEM STATEMENT

In this chapter, we first motivate our research by discussing both the benefits and the performance limitations with current VM technology. Then we present the general research framework conducted in this dissertation.

#### **3.1** Benefits of VM-based Computing Environments

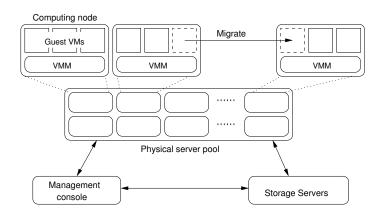

System management capabilities are increased for a VM-based environment – including allowing special configurations and online maintenance. To demonstrate this, Figure 3.1 illustrates a possible VM-based deployment. Each computing node in the physical server pool is running a hypervisor that hosts one or more VMs<sup>2</sup>. A set of VMs across the cluster form a virtual cluster, on which users can host their multitier data centers or parallel applications. There can be a management console which performs all management activities, including launching, checkpointing, or migrating VMs across the cluster. To prepare a virtual cluster with a special configuration, all that is required is to choose a set of physical servers and launch VMs with the desired configurations on those servers. This avoids the lengthy procedure of resetting

<sup>&</sup>lt;sup>2</sup>For performance-critical deployments such as HPC, each active VM runs on one or more dedicated cores, while more VMs can be consolidated on a single core for date centers.

all the physical hosts. More importantly, this does not affect other users using the same physical servers. Online maintenance is also simplified. To apply patches or update a physical node, system administrators no longer need to wait for application termination before taking them off-line. VMs on those servers can be migrated to other available physical nodes, reducing the administrative burden.

Figure 3.1: A possible deployment of HPC with virtual machines

Besides manageability, under certain circumstances VM environments can also lead to performance benefits. For example, with easy re-configuration it becomes much more practical to host HPC applications using customized, light-weight OSes. This concept of a customized OS has proven to be desirable for achieving increased performance in HPC [3, 13, 26, 34, 35]. VM migration can also help improve communication performance. For example, a parallel application may initially be scheduled onto several physical nodes far from each other in network topology due to node availability. But whenever possible, it is desirable to schedule the processes onto physical nodes near each other, which improves communication efficiency. Through VM migration, it is also possible to alleviate resource contention and thus achieve better resource utilization. For instance, VMs hosting computing jobs with a high volume of network I/O can be relocated with other VMs hosting more CPU intensive applications with less I/O requirements.

VM technology is also beneficial in many other aspects, including security, productivity, or debugging. Mergen et al. [34] have discussed in more detail the value of a VM-based HPC environment.

## 3.2 Performance Limitations of Current I/O Virtualization

While VM technology has shown its potential to relieve the manageability issues on large scale computing systems, concerns about performance block the community from embracing VM technologies in certain environments such as HPC. As we have discussed in Section 2.1, network I/O can incur high latency and high CPU utilization because of the VMM intervention. We find such overhead clearly observable in some cases.

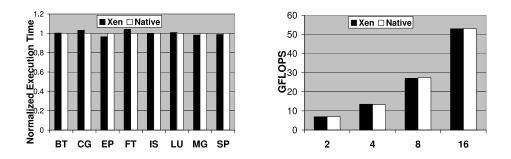

Figure 3.2: NAS Parallel Benchmarks

Figure 3.2 shows the performance of the NAS [39] Parallel Benchmark suite on 4 processes with MPICH [2] over TCP/IP. The processes are on 4 Xen DomUs, which are hosted on 4 physical machines. We compare the relative execution time with the same test on 4 nodes with native environment. For communication intensive benchmarks such as IS and CG, applications running in virtualized environments perform 12% and 17% worse, respectively. The EP benchmark, however, which is computation intensive with only a few barrier synchronizations, maintains the native level of performance. Table 3.1 illustrates the distribution of execution times collected by Xenoprof [33]. We find that for CG and IS, around 30% of the execution time is consumed by the isolated device domain (Dom0 in our case) and the Xen VMM for processing the network I/O operations. On the other hand, for the EP benchmark, 99% of the execution time is spent natively in the guest domain (DomU) due to a very low volume of communication. It should be noted that in this example, each physical node hosts only one DomU with one processor, even though the node is equipped with dual CPUs. If we run two DomUs per node to utilize both the CPUs, Dom0 starts competing for CPU resources with user domains when processing I/O requests, which leads to an even larger performance degradation as compared to the native case.

This example identifies I/O virtualization as the main bottleneck for virtualization, which leads to the observation that I/O virtualization with near-native performance would allow us to achieve application performance in VMs that rivals native environments.

|                     | Table 3.1: Distribution of execution time for NAS |       |                          |  |  |

|---------------------|---------------------------------------------------|-------|--------------------------|--|--|

|                     | $\mathrm{Dom}0$                                   | Xen   | $\mathrm{Dom}\mathrm{U}$ |  |  |

| CG                  | 16.6%                                             | 10.7% | 72.7%                    |  |  |

| IS                  | 18.1%                                             | 13.1% | 68.8%                    |  |  |

| $\mathbf{EP}$       | 00.6%                                             | 00.3% | 99.0%                    |  |  |

| BT                  | 06.1%                                             | 04.0% | 89.9%                    |  |  |

| $\operatorname{SP}$ | 09.7%                                             | 06.5% | 83.8%                    |  |  |

## 3.3 Proposed High Performance I/O Virtualization Framework

The main objective of our research is to reduce the overhead of network I/O in VM environments. We mainly focus on HPC systems, where performance is one of the most critical demands.

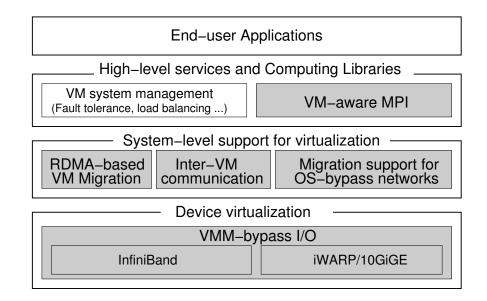

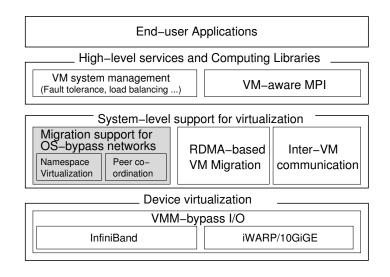

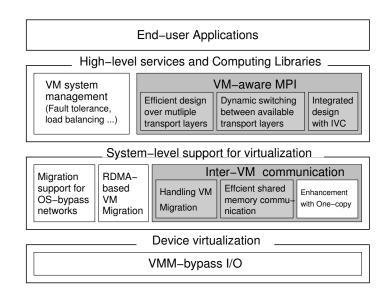

Figure 3.3 shows the various components of the proposed research framework. In general, we work on the shaded boxes. The un-shaded ones represents the system components that need not be changed (End-user Application), or are being studied by other related research and industrial efforts (VM System Management [38, 55, 60]), which will not be the focus of our study. As can be seen, we work on multiple aspects of the I/O subsystems. At the device virtualization layer, we propose VMM-bypass I/O, which leverages the OS-bypass nature of modern high speed interconnects and achieves close-to-native level network I/O performance. The migration support for VMM-bypass I/O is carried out at the system level. Also at system level, we propose high performance inter-VM communication, which is especially important since multicore systems are becoming ubiquitous. We also optimize the VM migration through RDMA, significantly reducing the management cost. On top of the system level, we work on high level services so that High End Computing (HEC) applications can transparently benefit from our research. We design a VM-aware MPI, which hides all the complexities of our research work from the end applications.

Figure 3.3: Proposed research framework

More specifically, we aim to address the following questions with this dissertation:

## • How can we reduce the network I/O virtualization overhead in modern computing systems featuring high speed interconnects?

To reduce the network I/O performance, we use a technique dubbed Virtual Machine Monitor bypass (VMM-bypass) I/O. VMM-bypass I/O extends the idea of OS-bypass I/O (as described in Section 2.2) in the context of VM environments. The key idea is that a guest module residing in the VM takes care of all the privileged accesses, such as creating the virtual access points (e.g. UAR for InfiniBand) and mapping them into the address space of the user processes. Thus a backend module provides such accesses for guest modules. This backend module can either reside in the device domain (such as Xen) or in the virtual machine monitor for other VM environments like VMware ESX server. The communication between the guest modules and the backend module is achieved through the inter-VM communication schemes provided by the VM environment. After the initial setup process, communication operations can be initiated directly from the user process. By removing the VMM from the critical path of communication, VMM-bypass I/O is able to achieve near-native I/O performance in VM environments. We will discuss VMM-bypass I/O in more details in Chapter 4.

# • How can we migrate network resources with VMM-bypass I/O capability?

The VMM-bypass I/O technique itself brings additional challenges. For example, migration is becoming difficult in such scenarios compared with VMs using traditional network devices such as Ethernet. First, the intelligent OS-bypass capable NICs manage large amounts of location-dependent resources which are kept transparent to both applications and operating systems and cannot be migrated with the VMs. This makes the existing solutions for current VM technologies, which target TCP/IP networks, less applicable. Further, applications in cluster environments using specialized interfaces of high speed interconnects typically expect reliable services at the NIC level. Thus, it is important to make migration transparent to applications and to avoid packet drops or out-of-order delivery during migration. We achieve migration of OS-bypass NICs by namespace virtualization and peer coordination, which will be described in detail in Chapter 5.

• How can we reduce the cost of inter-VM communication on the same physical host, which is especially important for multi-core architectures?

Efficient inter-VM communication is another key issue for reducing the I/O virtualization overhead especially when multi-core architecture is leading to a high degree of server consolidation. In VM environments, management activities such as migration occur at the level of entire VMs. Thus, all processes running in the same VM must be managed together. To achieve fine-grained process-level control, each computing process has to be hosted in a separate VM, and therefore, in a separate OS. This presents a problem, because processes in distinct OSes can no longer communicate via shared memory [8], even if they share a physical host. This restriction is undesirable because communication via shared memory is typically considered to be more efficient than network loopback and is being used in most MPI implementations [8, 43]. This inefficiency is magnified with the emergence of modern multi-core systems. We present efficient inter-VM communication, which allows shared memory communication even for computing processes in different VMs, in Chapter 6. A further enhancement to inter-VM communication via one-copy shared memory will be presented in Chapter 7.

• How can we design efficient middleware so that applications running in VM-based environments can benefit transparently from our research?

One philosophy for today's high performance virtualization techniques is paravirtualization, which allows certain changes to systems running in VM. Paravirtualization sacrifices transparency for performance. While it is always desirable to keep all design complexities away from end-user applications, application transparency is not always easy to achieve. For example, we propose our own APIs for the above-mentioned inter-VM communication. But in practice it is almost impossible to ask end applications to be modified to take advantage of it. As a result, our proposed techniques can be severely limited if we cannot make them transparent to end applications. Fortunately, most of today's HPC applications are written with a certain programming model. For parallel programming, MPI is the defacto standard. Most of the parallel HPC applications are written using MPI for communication among peer computing processes. As a result, by delivering an efficient MPI library which integrates our research, most applications can benefit while remaining unmodified. To achieve this goal, we design MVAPICH2, a high performance MPI2 library based by MPICH2 by extending the ADI3 laver. The goal of our design is to take advantage of the available communication methods on a cluster to achieve the best performance, such as shared memory for intra-node communication and InfiniBand for internode communication. We describe our design in Section 6.2.1.

MVAPICH2 can also run in VM environments, however, its default shared memory communication channel can no longer be used if computing processes are hosted on different VMs. Thus, we design MVAPICH2-ivc, which is able to use inter-VM communication in VM-based environments. We present our design in detail in Section 6.2.2.

• How can we further reduce the management overhead for VM-based computing environments by taking advantage of modern high speed interconnects?

To address this issue, we focus on VM migration in this dissertation, the basis for many management tasks in VM-based environments. We propose to use RDMA as the transfer mechanism for VM migration. RDMA can benefit VM migration in various aspects. First, with the extremely high throughput offered by high speed interconnects and RDMA, the time needed to transfer the memory pages can be reduced significantly, which leads to an immediate save on total VM migration time. Further, data communication over OS-bypass and RDMA does not need to involve CPUs, caches, or context switches. This allows migration to be carried out with minimum impact on guest operating systems and hosted applications. We discuss RDMA-based VM migration in Chapter 8.

## CHAPTER 4

# LOW OVERHEAD NETWORK I/O IN VIRTUAL MACHINES

In this chapter, we focus on reducing the network I/O virtualization overhead in VM environments, as well as its migration support. More specifically, we work on the highlighted part in Figure 4.1 of our proposed research framework.

Figure 4.1: Network I/O in proposed research framework

We propose VMM-bypass I/O in Section 4.1, which achieves native-level network I/O by taking advantage of the OS-bypass features available on most modern high

speed interconnects. We then discuss XenIB in Sections 4.2 and 4.3, which implements VMM-bypass I/O in Xen over InfiniBand. Finally, we carry out a performance evaluation in Section 4.4.

## 4.1 VMM-bypass I/O

VMM-bypass I/O can be viewed as an extension of the idea of OS-bypass I/O in the context of VM environments. In this section, we describe the basic design of VMM-bypass I/O. Two key ideas in our design are *para-virtualization* and *high-level virtualization*.

In some VM environments, I/O devices are virtualized at hardware level [57]. Each I/O instruction to access a device is virtualized by the VMM. With this approach, existing device drivers can be used in guest VMs without any modification. However, it significantly increases the complexity of virtualizing devices. For example, one popular InfiniBand HCA (MT23108 from Mellanox [32]) presents itself as a PCI-X device to the system. After initialization, it can be accessed by OS using memory mapped I/O. Virtualizing this device at hardware level would require us not only understand all hardware commands issued through memory mapped I/O, but also implement virtual PCI-X bus in guest VMs. Another problem with this approach is performance. Since existing physical devices are typically not designed to run in a virtualized environment, the interfaces presented at the hardware level may exhibit significant performance degradation when they are virtualized.

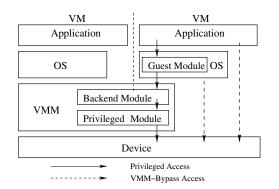

Our VMM-bypass I/O virtualization design is based on the idea of para-virtualization, similar to [12] and [71]. We do not preserve hardware interfaces of existing devices. To virtualize a device in a guest VM, we implement a device driver called a *guest module*  in guest OS. The guest module is responsible for handling all privileged accesses to the device. In order to achieve VMM-bypass device access, the guest module also needs to set things up properly so that I/O operations can be carried out directly in the guest VM. This means that the guest module must be able to create virtual access points on behalf of the guest OS and map them into the addresses of user processes. Since the guest module does not have direct access to the device hardware, we need to introduce another software component called *backend module*, which provides device hardware access for different guest modules. If devices are accessed inside the VMM, the backend module can be implemented as part of the VMM. It is possible to let the backend module talk to the device directly. However, we can greatly simplify its design by reusing the original privilege module of the OS-bypass device driver. In addition to serving as a proxy for device hardware access, the backend module also coordinates accesses among different VMs so that system integrity can be maintained. The VMM-bypass I/O design is illustrated in Figure 4.2.

Figure 4.2: VMM-bypass (I/O Handled by VMM Directly)

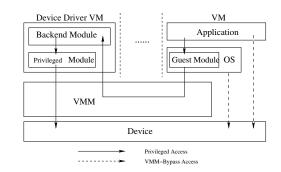

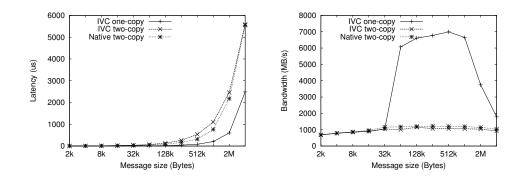

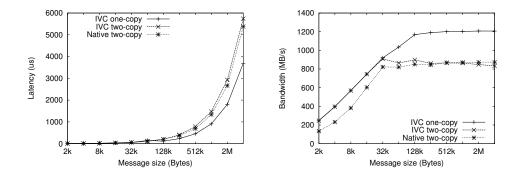

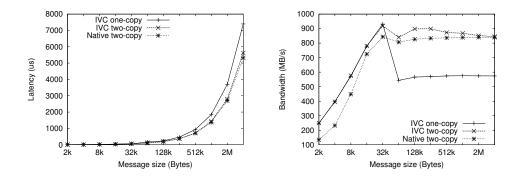

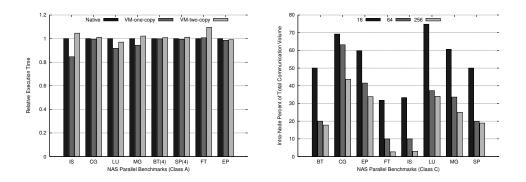

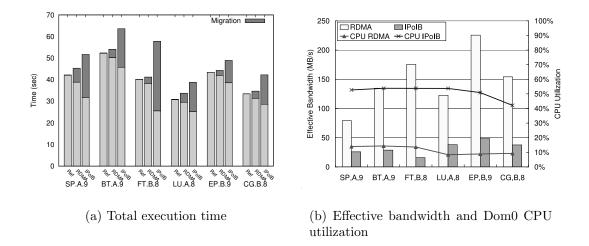

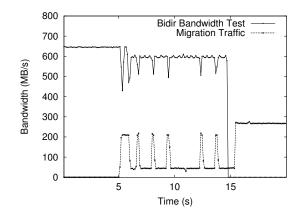

If device accesses are provided by another VM (device driver VM), the backend module can be implemented within the device driver VM. The communication between guest modules and the backend module can be achieved through the inter-VM communication mechanism provided by the VM environment. This approach is shown in Figure 4.3.