# HIGH PERFORMANCE AND SCALABLE MPI INTRA-NODE COMMUNICATION MIDDLEWARE FOR MULTI-CORE CLUSTERS

DISSERTATION

Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University

By

Lei Chai, Master of Science

\* \* \* \* \*

The Ohio State University

2009

Dissertation Committee:

Prof. D. K. Panda, Adviser

Prof. P. Sadayappan

Prof. F. Qin

Approved by

Adviser Graduate Program in Computer Science and Engineering © Copyright by

Lei Chai

2009

## ABSTRACT

Cluster of workstations is one of the most popular architectures in high performance computing, thanks to its cost-to-performance effectiveness. As multi-core technologies are becoming mainstream, more and more clusters are deploying multicore processors as the build unit. In the latest Top500 supercomputer list published in November 2008, about 85% of the sites use multi-core processors from Intel and AMD. Message Passing Interface (MPI) is one of the most popular programming models for cluster computing. With increased deployment of multi-core systems in clusters, it is expected that considerable communication will take place within a node. This suggests that MPI intra-node communication is going to play a key role in the overall application performance.

This dissertation presents novel MPI intra-node communication designs, including user level shared memory based approach, kernel assisted direct copy approach, and efficient multi-core aware hybrid approach. The user level shared memory based approach is portable across operating systems and platforms. The processes copy messages into and from a shared memory area for communication. The shared buffers are organized in a way such that it is efficient in cache utilization and memory usage. The kernel assisted direct copy approach takes help from the operating system kernel and directly copies message from one process to another so that it only needs one copy and improves performance from the shared memory based approach. In this approach, the memory copy can be either CPU based or DMA based. This dissertation explores both directions and for DMA based memory copy, we take advantage of novel mechanism such as I/OAT to achieve better performance and computation and communication overlap. To optimize performance on multicore systems, we efficiently combine the shared memory approach and the kernel assisted direct copy approach and propose a topology-aware and skew-aware hybrid approach. The dissertation also presents comprehensive performance evaluation and analysis of the approaches on contemporary multi-core systems such as Intel Clovertown cluster and AMD Barcelona cluster, both of which are quad-core processors based systems.

Software developed as a part of this dissertation is available in MVAPICH and MVAPICH2, which are popular open-source implementations of MPI-1 and MPI-2 libraries over InfiniBand and other RDMA-enabled networks and are used by several hundred top computing sites all around the world. Dedicated to My Family

### ACKNOWLEDGMENTS

I would like to thank my adviser, Prof. D. K. Panda for guiding me throughout the duration of my PhD study. I'm thankful for all the efforts he took for my dissertation. I would like to thank him for his friendship and counsel during the past years.

I would like to thank my committee members Prof. P. Sadayappan and Prof. F. Qin for their valuable guidance and suggestions.

I'm especially grateful to have had Dr. Jiesheng Wu as a mentor during my first year of graduate study. I'm also grateful to Donald Traub and Spencer Shepler for their guidance and advice during my internships at Sun Microsystems.

I would like to thank all my senior Nowlab members for their patience and guidance, Dr. Pavan Balaji, Weihang Jiang, Dr. Hyun-Wook Jin, Dr. Jiuxing Liu, Dr. Amith Mamidala, Dr. Sundeep Narravula, Dr. Ranjit Noronha, Dr. Sayantan Sur, Dr. Karthik Vaidyanathan, Dr. Abhinav Vishnu, and Dr. Weikuan Yu. I would also like to thank all my colleagues, Krishna Chaitanya, Tejus Gangadharappa, Karthik Gopalakrishnan, Wei Huang, Matthew Koop, Ping Lai, Greg Marsh, Xiangyong Ouyang, Jonathan Perkins, Ajay Sampat, Gopal Santhanaraman, Jaidev Sridhar, and Hari Subramoni. I'm especially grateful to Sayantan, Jin, Wei, Matt, and Weikuan and I'm lucky to have worked closely with them on different projects. During all these years, I met many people at Ohio State, some of whom become very close friends, and I'm thankful for their friendship.

Finally, I would like to thank my family members, my husband Guoqiang, my son Terry, my dad and my mom. I would not have had made it this far without their love and support.

## VITA

| April 22, 1980               | Born - Qingdao, China.                                                                 |

|------------------------------|----------------------------------------------------------------------------------------|

| September 1999 - June 2003   | B. Engr. Computer Science and<br>Engineering, Zhejiang University,<br>Hangzhou, China. |

| September 2003 - August 2004 | Distinguished University Fellow,<br>The Ohio State University.                         |

| October 2004 - December 2007 | Graduate Research Associate,<br>The Ohio State University.                             |

| June 2006 - September 2006   | Summer Intern,<br>Sun Microsystems, Austin, TX.                                        |

| June 2007 - September 2007   | Summer Intern,<br>Sun Microsystems, Menlo Park, CA.                                    |

| January 2008 - December 2008 | Distinguished University Fellow,<br>The Ohio State University.                         |

| January 2009 - March 2009    | Graduate Research Associate,<br>The Ohio State University.                             |

## PUBLICATIONS

L. Chai, P. Lai, H.-W. Jin and D. K. Panda, "Designing An Efficient Kernel-level and User-level Hybrid Approach for MPI Intra-node Communication on Multi-core Systems", International Conference on Parallel Processing (ICPP 2008), Sept. 2008.

L. Chai, X. Ouyang, R. Noronha and D.K. Panda, "pNFS/PVFS2 over InfiniBand: Early Experiences", Petascale Data Storage Workshop 2007, in conjunction with SuperComputing (SC) 2007, Reno, NV, November 2007. H. -W. Jin, S. Sur, L. Chai, D. K. Panda, "Lightweight Kernel-Level Primitives for High-Performance MPI Intra-Node Communication over Multi-Core Systems", IEEE Cluster 2007 (Poster), Austin, TX, September 2007.

K. Vaidyanathan, L. Chai, W. Huang and D. K. Panda, "Efficient Asynchronous Memory Copy Operations on Multi-Core Systems and I/OAT", IEEE Cluster 2007, Austin, TX, September 2007.

R. Noronha, L. Chai, T. Talpey and D. K. Panda, "Designing NFS With RDMA For Security, Performance and Scalability", The 2007 International Conference on Parallel Processing (ICPP-07), Xi'an, China.

S. Sur, M. Koop, L. Chai and D. K. Panda, "Performance Analysis and Evaluation of Mellanox ConnectX InfiniBand Architecture with Multi-Core Platforms", 15th Symposium on High-Performance Interconnects (HOTI-15), August 2007.

L. Chai, Q. Gao and D. K. Panda, "Understanding the Impact of Multi-Core Architecture in Cluster Computing: A Case Study with Intel Dual-Core System", The 7th IEEE International Symposium on Cluster Computing and the Grid (CCGrid 2007), May 2007.

L. Chai, A. Hartono and D. K. Panda, "Designing High Performance and Scalable MPI Intra-node Communication Support for Clusters", The IEEE International Conference on Cluster Computing (Cluster 2006), September 2006.

L. Chai, R. Noronha and D. K. Panda, "MPI over uDAPL: Can High Performance and Portability Exist Across Architectures?", The 6th IEEE International Symposium on Cluster Computing and the Grid (CCGrid 2006), May 2006.

S. Sur, L. Chai, H.-W. Jin and D. K. Panda, "Shared Receive Queue Based Scalable MPI Design for InfiniBand Clusters", International Parallel and Distributed Processing Symposium (IPDPS 2006), April 25-29, 2006, Rhodes Island, Greece.

S. Sur, H.-W. Jin, L. Chai and D. K. Panda, "RDMA Read Based Rendezvous Protocol for MPI over InfiniBand: Design Alternatives and Benefits", Symposium on Principles and Practice of Parallel Programming (PPOPP 2006), March 29-31, 2006, Manhattan, New York City.

L. Chai, R. Noronha, P. Gupta, G. Brown, and D. K. Panda, "Designing a Portable MPI-2 over Modern Interconnects Using uDAPL Interface", EuroPVM/MPI 2005, Sept. 2005.

H.-W. Jin, S. Sur, L. Chai and D. K. Panda, "LiMIC: Support for High-Performance MPI Intra-Node Communication on Linux Clusters", International Conference on Parallel Processing (ICPP-05), June 14-17, 2005, Oslo, Norway.

L. Chai, S. Sur, H.-W. Jin and D. K. Panda, "Analysis of Design Considerations for Optimizing Multi-Channel MPI over InfiniBand", Workshop on Communication Architecture for Clusters (CAC 2005); In Conjunction with IPDPS, April 4-8, 2005, Denver, Colorado.

## FIELDS OF STUDY

Major Field: Computer Science and Engineering

Studies in:

| Computer Architecture | Prof. D. K. Panda |

|-----------------------|-------------------|

| Computer Networks     | Prof. D. Xuan     |

| Software Systems      | Prof. G. Agrawal  |

# TABLE OF CONTENTS

| Abst | ract .              |                                   |                                                                                                     | ii                   |

|------|---------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|

| Dedi | catior              | 1                                 | i                                                                                                   | iv                   |

| Ackr | nowled              | lgments                           |                                                                                                     | v                    |

| Vita |                     |                                   |                                                                                                     | ii                   |

| List | of Tal              | oles                              |                                                                                                     | v                    |

| List | of Fig              | gures .                           |                                                                                                     | v                    |

| Chap | oters:              |                                   |                                                                                                     |                      |

| 1.   | Intro               | duction                           |                                                                                                     | 1                    |

|      | $1.1 \\ 1.2 \\ 1.3$ | MPI II                            | ectures of Multi-core Clusters                                                                      |                      |

|      | 1.5 $1.4$           |                                   |                                                                                                     | .3                   |

|      | 1.5                 | Dissert                           | ation Overview                                                                                      | 6                    |

| 2.   | Unde                | erstandi                          | ng the Communication Characteristics on Multi-core Clusters 1                                       | .8                   |

|      | 2.1                 | Design<br>2.1.1<br>2.1.2<br>2.1.3 | Programming Model and Benchmarks                                                                    | .9<br>.9<br>.9<br>.1 |

|      | 2.2                 | Perform<br>2.2.1<br>2.2.2         | nance Evaluation       2         Latency and Bandwidth       2         Message Distribution       2 |                      |

|    |      | 2.2.3 Potential Cache and Memory Contention                      | 30 |

|----|------|------------------------------------------------------------------|----|

|    |      | 2.2.4 Benefits of Data Tiling                                    | 31 |

|    |      | 2.2.5 Scalability                                                | 32 |

|    | 2.3  | Summary                                                          | 33 |

| 3. | Shar | ed Memory Based Design                                           | 35 |

|    | 3.1  | Basic Shared Memory Based Design                                 | 35 |

|    |      | 3.1.1 Design                                                     | 36 |

|    |      | 3.1.2 Optimization for NUMA systems                              | 38 |

|    |      | 3.1.3 Exploiting Processor Affinity                              | 39 |

|    | 3.2  | Advanced Shared Memory Based Design                              | 39 |

|    |      | 3.2.1 Overall Architecture                                       | 39 |

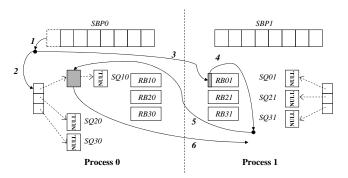

|    |      | 3.2.2 Message Transfer Schemes                                   | 41 |

|    |      | 3.2.3 Analysis of the Design                                     | 44 |

|    |      | 3.2.4 Optimization Strategies                                    | 47 |

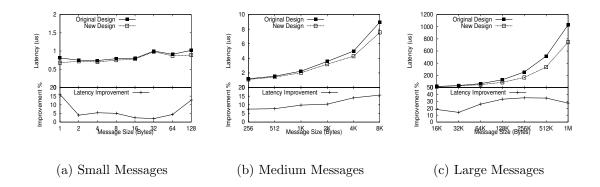

|    | 3.3  | Performance Evaluation                                           | 48 |

|    |      | 3.3.1 Latency and Bandwidth on NUMA Cluster                      | 49 |

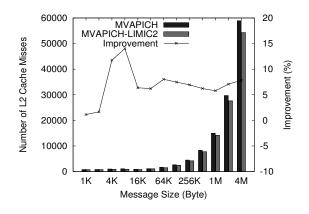

|    |      | 3.3.2 L2 Cache Miss Rate                                         | 50 |

|    |      | 3.3.3 Impact on MPI Collective Functions                         | 50 |

|    |      | 3.3.4 Latency and Bandwidth on Dual Core NUMA Cluster            | 52 |

|    |      | 3.3.5 Application Performance on Intel Clovertown Cluster        | 53 |

|    | 3.4  | Summary                                                          | 54 |

| 4. | CPU  | Based Kernel Assisted Direct Copy                                | 56 |

|    | 4.1  | Limitations of the Existing Approach and Overall Design of LiMIC | 57 |

|    |      | 4.1.1 Kernel-Based Memory Mapping                                | 57 |

|    |      | 4.1.2 Our Approach: LiMIC                                        | 58 |

|    | 4.2  | Design and Implementation Issues                                 | 60 |

|    |      | 4.2.1 Portable and MPI Friendly Interface                        | 60 |

|    |      | 4.2.2 Memory Mapping Mechanism                                   |    |

|    |      | 4.2.3 Copy Mechanism                                             | 63 |

|    |      | 4.2.4 MPI Message Matching                                       | 64 |

|    | 4.3  | Performance Evaluation                                           | 65 |

|    |      | 4.3.1 Performance Evaluation of LiMIC on a Single-core Cluster . | 65 |

|    |      | 4.3.2 Application Performance of LiMIC2 on an AMD                |    |

|    |      | Barcelona System                                                 | 74 |

|    |      | 4.3.3 Performance Impact on MPI+OpenMP Model                     | 74 |

|    | 4.4  | Summary                                                          | 76 |

| 5. | DM    | A Based Kernel Assisted Direct Copy                                                                                                    |

|----|-------|----------------------------------------------------------------------------------------------------------------------------------------|

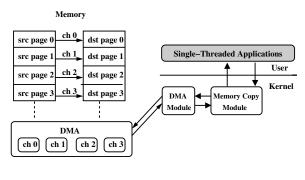

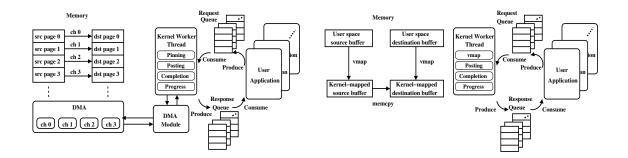

|    | 5.1   | Design of the DMA Based Schemes795.1.1SCI (Single-Core with I/OAT)79                                                                   |

|    |       | 5.1.2 MCI (Multi-Core with I/OAT) $\ldots \ldots \ldots \ldots \ldots 80$                                                              |

|    |       | 5.1.3 MCNI (Multi-Core with No I/OAT) 82                                                                                               |

|    | 5.2   | Integration with MVAPICH                                                                                                               |

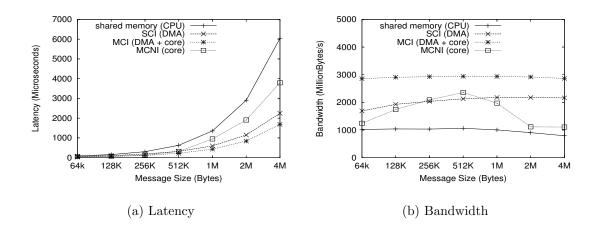

|    | 5.3   | Performance Evaluation                                                                                                                 |

|    | 5.4   | Summary                                                                                                                                |

| 6. | Effic | ient Kernel-level and User-level Hybrid Approach                                                                                       |

|    | 6.1   | Introduction of LiMIC2                                                                                                                 |

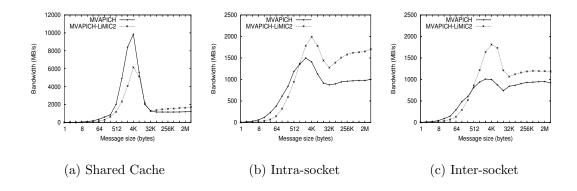

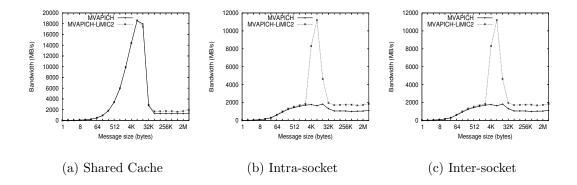

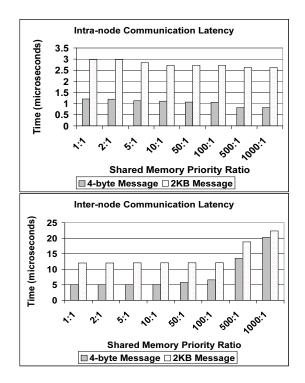

|    | 6.2   | Initial Performance Evaluation and Analysis: Micro-Benchmarks . 91                                                                     |

|    |       | 6.2.1 Impact of Processor Topology                                                                                                     |

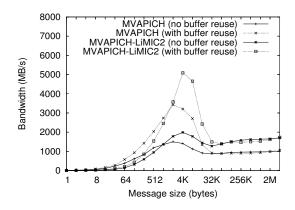

|    |       | 6.2.2 Impact of Buffer Reuse                                                                                                           |

|    |       | 6.2.3 L2 Cache Utilization                                                                                                             |

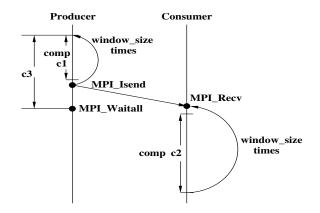

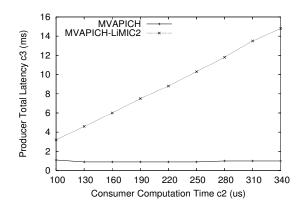

|    |       | 6.2.4 Impact of Process Skew                                                                                                           |

|    | 6.3   | Designing the Hybrid Approach                                                                                                          |

|    |       | 6.3.1 Topology Aware Thresholds                                                                                                        |

|    |       | 6.3.2 Skew Aware Thresholds                                                                                                            |

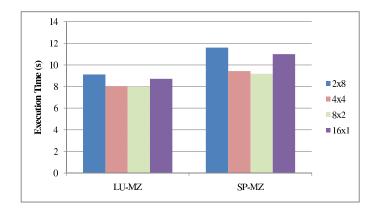

|    | 6.4   | Performance Evaluation with Collectives and Applications 102                                                                           |

|    |       | 6.4.1 Impact on Collectives                                                                                                            |

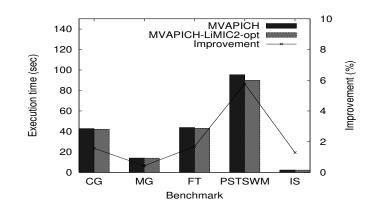

|    |       | 6.4.2 Impact on Applications                                                                                                           |

|    | 6.5   | Summary                                                                                                                                |

| 7. | Ana   | lysis of Design Considerations for Multi-channel MPI                                                                                   |

|    | 7.1   | Channel polling                                                                                                                        |

|    |       | 7.1.1 Channel polling overheads                                                                                                        |

|    |       | 7.1.2 Channel polling schemes                                                                                                          |

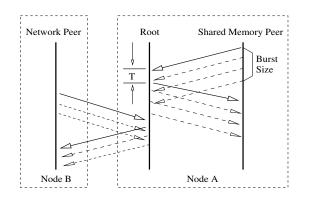

|    | 7.2   | Channel thresholds                                                                                                                     |

|    |       | 7.2.1 Communication startup and message transmission                                                                                   |

|    |       | overheads $\ldots \ldots 114$ |

|    |       | 7.2.2 Threshold decision methodology                                                                                                   |

|    | 7.3   | Performance Evaluation                                                                                                                 |

|    |       | 7.3.1 Evaluation of Polling Schemes                                                                                                    |

|    |       | 7.3.2 Evaluation of Thresholds                                                                                                         |

|    | 7.4   | Summary                                                                                                                                |

|    |       |                                                                                                                                        |

| 8.     | Oper  | 1 Source | e Software Release and its Impact                          |

|--------|-------|----------|------------------------------------------------------------|

| 9.     | Conc  | lusions  | and Future Research Directions                             |

|        | 9.1   | Summa    | ary of Research Contributions                              |

|        |       | 9.1.1    | High Performance and Scalable MPI Intra-node Communi-      |

|        |       |          | cation Designs                                             |

|        |       | 9.1.2    | Multi-core Aware Optimizations                             |

|        |       | 9.1.3    | Comprehensive Analysis of Considerations for Multi-channel |

|        |       |          | MPI                                                        |

|        |       | 9.1.4    | In-depth Understanding of Application Behaviors on Multi-  |

|        |       |          | core Clusters                                              |

|        | 9.2   | Future   | Research Directions                                        |

| יו וים |       | 1        | 190                                                        |

| BIDII  | ograp | ony      |                                                            |

# LIST OF TABLES

## Table

## Page

| 2.1 | Message Distribution in NAS Benchmarks Class B on 16 Cores              | 27  |

|-----|-------------------------------------------------------------------------|-----|

| 2.2 | Message Distribution in NAS Benchmarks Class C on 256 Cores $\ . \ .$ . | 29  |

| 4.1 | b_eff Results Comparisons (MB/s)                                        | 71  |

| 4.2 | Intra-Node Message Size Distribution for IS Class A                     | 73  |

| 5.1 | Basic Interfaces for Using I/OAT Copy Engine                            | 80  |

| 5.2 | Kernel Module Interfaces for IPC                                        | 83  |

| 5.3 | Message Size Distribution of MPI benchmarks                             | 87  |

| 6.1 | Message Size Distribution (Single Node 1x8)                             | 106 |

# LIST OF FIGURES

| Figu | Figure Pag                                                         |     |

|------|--------------------------------------------------------------------|-----|

| 1.1  | Illustration of Multi-Core Cluster                                 | 5   |

| 1.2  | Memory Transactions for Different Intra-Node Communication Schemes | 5 7 |

| 1.3  | Problem Space of this Dissertation                                 | 11  |

| 2.1  | Latency and Bandwidth in Multi-core Cluster                        | 23  |

| 2.2  | Message Distribution of NAMD on 16 Cores                           | 24  |

| 2.3  | Message Distribution of HPL on 16 Cores                            | 24  |

| 2.4  | Message Distribution of HPL on 256 Cores                           | 28  |

| 2.5  | Application Performance on Different Configurations                | 29  |

| 2.6  | Effect of Data Tiling                                              | 30  |

| 2.7  | Application Scalability                                            | 33  |

| 3.1  | Basic Shared Memory Based Design                                   | 36  |

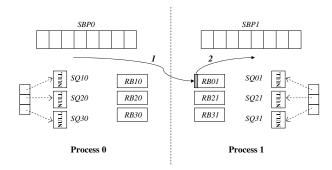

| 3.2  | Overall Architecture of the Proposed Design                        | 40  |

| 3.3  | Send/Receive Mechanism for a Small Message                         | 42  |

| 3.4  | Send/Receive Mechanism for a Large Message                         | 42  |

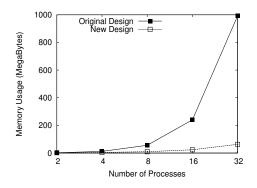

| 3.5  | Memory Usage of the Proposed New Design Within a Node              | 46  |

| 3.6  | Latency on NUMA Cluster                                                        | 49 |

|------|--------------------------------------------------------------------------------|----|

| 3.7  | Bandwidth on NUMA Cluster                                                      | 51 |

| 3.8  | L2 Cache Miss Rate                                                             | 51 |

| 3.9  | MPI_Barrier Performance                                                        | 51 |

| 3.10 | MPI_Alltoall Performance                                                       | 51 |

| 3.11 | Latency on Dual Core NUMA Cluster                                              | 52 |

| 3.12 | Bandwidth on Dual Core NUMA Cluster                                            | 53 |

| 3.13 | Application Performance Comparison                                             | 54 |

| 4.1  | Approaches for Kernel-Based Design                                             | 59 |

| 4.2  | Memory Mapping Mechanism                                                       | 62 |

| 4.3  | MPI Level Latency and Bandwidth                                                | 68 |

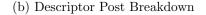

| 4.4  | LiMIC Cost Breakdown (Percentage of Overall Overhead) $\ . \ . \ .$ .          | 69 |

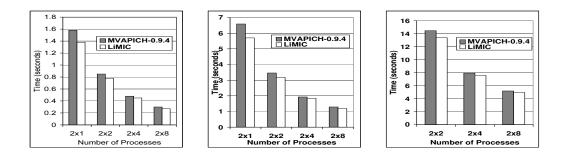

| 4.5  | IS Total Execution Time Comparisons: (a) Class A, (b) Class B, and (c) Class C | 71 |

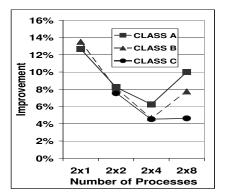

| 4.6  | IS Performance Improvement                                                     | 73 |

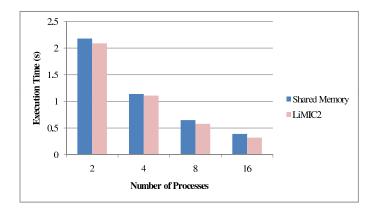

| 4.7  | Application Performance of LiMIC2 on an AMD Barcelona System .                 | 74 |

| 4.8  | Performance Impact on MPI+OpenMP Model                                         | 76 |

| 5.1  | Copy Engine Architecture and SCI Scheme                                        | 81 |

| 5.2  | Asynchronous Memory Copy Operations: (a) MCI Scheme and (b)<br>MCNI Scheme     | 81 |

| 5.3  | MPI-level Latency and Bandwidth                                                | 86 |

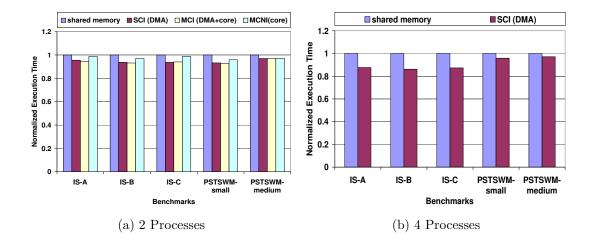

| 5.4  | MPI Application Performance                                                    | 87 |

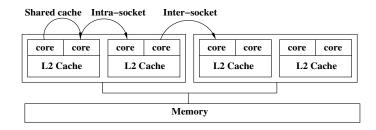

| 6.1  | Illustration of Intel Clovertown Processor                                                 |

|------|--------------------------------------------------------------------------------------------|

| 6.2  | Multi-pair Bandwidth                                                                       |

| 6.3  | Impact of Buffer Reuse (Intra-socket)                                                      |

| 6.4  | L2 Cache Misses                                                                            |

| 6.5  | Process Skew Benchmark                                                                     |

| 6.6  | Impact of Process Skew                                                                     |

| 6.7  | Multi-pair Bandwidth with Topology Aware Thresholds 100                                    |

| 6.8  | Impact of Skew Aware Thresholds                                                            |

| 6.9  | Collective Results (Single Node 1x8)                                                       |

| 6.10 | Application Performance (Single Node 1x8)                                                  |

| 6.11 | L2 Cache Misses in Applications (Single Node 1x8) $\ldots \ldots \ldots \ldots \ldots 105$ |

| 6.12 | Application Performance on 8 nodes (8x8)                                                   |

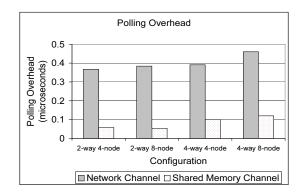

| 7.1  | Polling overhead of network channel and shared memory channel 110                          |

| 7.2  | Latency of static polling scheme                                                           |

| 7.3  | Message discovery microbenchmark                                                           |

| 7.4  | Message discovery time of dynamic polling scheme                                           |

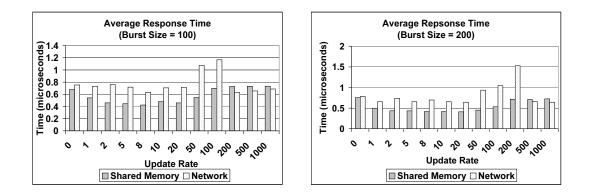

| 7.5  | Latency and bandwidth comparisons                                                          |

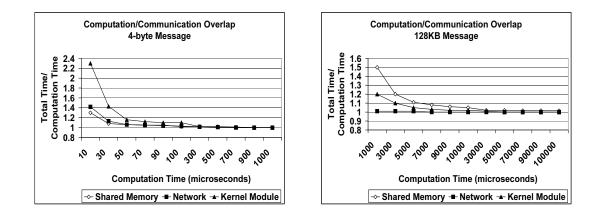

| 7.6  | Computation/communication overlap                                                          |

## CHAPTER 1

#### INTRODUCTION

The pace people pursuing computing power has never slowed down. Moore's Law has been proven to be true over the passage of time - the performance of microchips has been increasing at an exponential rate, doubling every two years. "In 1978, a commercial flight between New York and Paris cost around \$900 and took seven hours. If the principles of Moore's Law had been applied to the airline industry the way they have to the semiconductor industry since 1978, that flight would now cost about a penny and take less than one second." (a statement from Intel) However, it becomes more difficult to speedup processors nowadays by increasing frequency. One major barrier is the overheat problem, which high-frequency CPU must deal with carefully. The other issue is power consumption. These concerns make it less cost-to-performance effective to increase processor clock rate. Therefore, computer architects have designed *multi-core* processor, which means to place two or more processing cores on the same chip [29]. Multi-core processors speedup application performance by dividing the workload to different cores. It is also referred to as *Chip Multiprocessor* (CMP).

On the other hand, clusters [4] have been one of the most popular environments in parallel computing for decades. The emergence of multi-core architecture has brought clusters into a multi-core era. As a matter of fact, multi-core processors have already been widely deployed in parallel computing. In the Top500 supercomputer list published in 2007, more than 77% processors are multi-core processors from Intel and AMD [24]. This number becomes 85% in the latest Top500 list published in November, 2008.

Message Passing Interface (MPI) [61] is one of the most popular programming models for cluster computing. With the rapid deployment of multi-core systems in clusters, more and more communication will take place inside a node, which means MPI intra-node communication will play a critical role to the overall application performance.

MVAPICH [15] is an MPI library that delivers high performance, scalability and fault tolerance for high-end computing systems and servers using InfiniBand [6], iWARP [13] and other RDMA-enabled [67] interconnect networking technologies. MVAPICH2 is MPI-2 [62] compliant. MVAPICH and MVAPICH2 are being used by more than 840 organizations world-wide to extract the potential of these emerging networking technologies for modern systems.

In this dissertation we use MVAPICH as the framework and explore the alternatives of designing MPI intra-node communication, come up with optimization strategies for multi-core clusters, and study on the factors that affect MPI intranode communication performance. Further, we conduct in-depth evaluation and analysis on application characteristics on multi-core clusters. The rest of the chapter is organized as follows. First we provide an overview of the architectures of multi-core processors. Then we introduce the basic MPI intranode communication schemes. Following that we present the problem statement and our research approaches. And finally we provide an overview of this dissertation.

#### **1.1** Architectures of Multi-core Clusters

Multi-core means to integrate two or more complete computational cores within a single chip [29]. The motivation of the development of multi-core processors is the fact that scaling up processor speed results in dramatic rise in power consumption and heat generation. In addition, it becomes more difficult to increase processor speed nowadays that even a little increase in performance will be costly. Realizing these factors, computer architects have proposed multi-core processors that speed up application performance by dividing the workload among multiple processing cores instead of using one "super fast" single processor. Multi-core processor is also referred to as *Chip Multiprocessor* (CMP). Since a processing core can be viewed as an independent processor, in this proposal we use *processor* and *core* interchangeably.

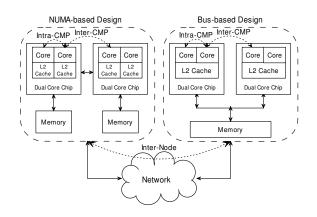

Most processor venders have multi-core products, e.g. Intel Quad-core [11] and Dual-core [9] Xeon, AMD Quad-core [21] and Dual-core Opteron [3], Sun Microsystems UltraSPARC T1 (8 cores) [25], IBM Cell [23], etc. There are various alternatives in designing cache hierarchy organization and memory access model. Figure 1.1 illustrates two typical multi-core system designs. The left box shows a NUMA [1] based dual-core system in which each core has its own L2 cache. Two cores on the same chip share the memory controller and local memory. Processors can also access remote memory, although local memory access is much faster. The right box shows a bus based dual-core system, in which two cores on the same chip share the same L2 cache and memory controller, and all the cores access the main memory through a shared bus. Intel Woodcrest processors [12] belong to this architecture. Intel Clovertown processors (quad-core) [7] are made of two Woodcrest processors. There are more advanced systems emerging recently, e.g. AMD Barcelona quad-core processors, in which four cores on the same chip have their own L2 caches but share the same L3 cache. The L3 cache is not a traditional inclusive cache, when data is loaded from the L3 cache to the L1 cache (L2 is always bypassed) the data can be removed from L3 or remain there depending on whether other cores are likely to access the data in the future. In addition, the L3 cache doesn't load data from the memory, it acts like a spill-over cache for items evicted from the L2 cache.

NUMA is a computer memory design where the memory access time depends on the memory location relative to a processor. Under NUMA, memory is shared between processors, but a processor can access its own local memory faster than non-local memory. Therefore, data locality is critical to the performance of an application. AMD systems are mostly based on NUMA architecture. Modern operating systems allocate memory in a NUMA-aware manner. Memory pages are always physically allocated local to processors where they are first touched, unless the desired memory is not available. Solaris has been supporting NUMA architecture for a number of years [71]. Linux also started to be NUMA-aware from 2.6 kernel. In our work so far we focus on Linux.

Due to its greater computing power and cost-to-performance effectiveness, multicore processor has been deployed in cluster computing. In a multi-core cluster, there are three levels of communication as shown in Figure 1.1. The communication

Figure 1.1: Illustration of Multi-Core Cluster

between two processors on the same chip is referred to as *intra-CMP communication* in this proposal. The communication across chips but within a node is referred to as *inter-CMP communication*. And the communication between two processors on different nodes is referred to as *inter-node communication*.

Multi-core cluster imposes new challenges in software design, both on middleware level and application level. How to design multi-core aware parallel programs and communication middleware to get optimal performance is a hot topic. There have been studies on multi-core systems. Koop, et al in [53] have evaluated the memory subsystem of Bensley platform using microbenchmarks. Alam, et al have done a scientific workloads characterization on AMD Opteron based multi-core systems [40]. Realizing the importance and popularity of multi-core architectures, researchers start to propose techniques for application optimization on multi-core systems. Some of the techniques are discussed in [36], [42], and [73]. Discussions of OpenMP on multi-core processors can be found in [39].

### 1.2 MPI Intra-node Communication

MPI stands for Message Passing Interface [61]. It is the *de facto* standard used for cluster computing. There are multiple MPI libraries in addition to MVAPICH, such as MPICH [45], MPICH2 [16], OpenMPI [17], HP MPI [5], Intel MPI [10], etc. Most clusters are built with multi-processor systems which means inter-node and intra-node communication co-exists in cluster computing. In this section we introduce the basic approaches for MPI intra-node communication.

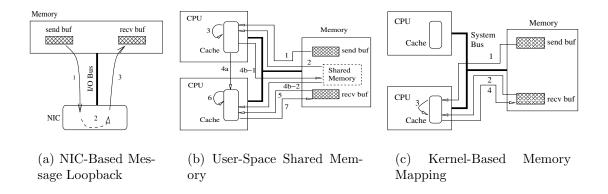

#### NIC-Based Message Loopback

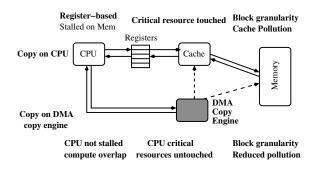

An intelligent NIC can provide a NIC-based loopback. When a message transfer is initiated, the NIC can detect whether the destination is on the same physical node or not. By initiating a local DMA from the NIC memory back to the host memory as shown in Figure 1.2(a), we can eliminate overheads on the network link because the message is not injected into the network. However, there still exist two DMA operations. Although I/O buses are getting faster, the DMA overhead is still high. Further, the DMA operations cannot utilize the cache effect.

InfiniHost [59] is a Mellanox's second generation InfiniBand Host Channel Adapter (HCA). It provides internal loopback for packets transmitted between two Queue Pairs (connections) that are assigned to the same HCA port. Most of other high-speed interconnections such as Myrinet [27] and Quadrics [64] also provide NIC-based message loopback. Ciaccio [32] also utilized NIC-level loopback to implement an efficient memcpy().

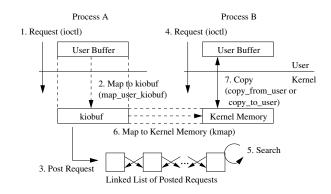

Figure 1.2: Memory Transactions for Different Intra-Node Communication Schemes

#### **User-Space Shared Memory**

This design alternative involves each MPI process on a local node, attaching itself to a shared memory region. This shared memory region can then be used amongst the local processes to exchange messages and other control information. The sending process copies the message to the shared memory area. The receiving process can then copy over the message to its own buffer. This approach involves minimal setup overhead for every message exchange and shows better performance for small and medium message sizes than NIC-level message loopback.

Figure 1.2(b) shows the various memory transactions which happen during the message transfer. In the first memory transaction labeled as 1; the MPI process needs to bring the send buffer to the cache. The second operation is a write into the shared memory buffer, labeled as 3. If the block of shared memory is not in cache, another memory transaction, labeled as 2 will occur to bring the block in cache. After this, the shared memory block will be accessed by the receiving MPI

process. The memory transactions will depend on the policy of the cache coherency implementation and can result in either operation 4a or 4b-1 followed by 4b-2. Then the receiving process needs to write into the receive buffer, operation labeled as 6. If the receive buffer is not in cache, then it will result in operation labeled as 5. Finally, depending on the cache block replacement scheme, step 7 might occur. It is to be noted that there are at least two copies involved in the message exchange. This approach might tie down the CPU with memory copy time. In addition, as the size of the message grows, the performance deteriorates because vigorous copy-in and copy-out also destroys the cache contents for the end MPI application.

This shared memory based design has been used in MPICH-GM [63] and other MPI implementations such as MVAPICH [15]. In addition, Lumetta et al. [56] have dealt with efficient design of shared memory message passing protocol and multiprotocol implementation. MPICH-Madeleine [26] and MPICH-G2 [41, 52] also have suggested multi-protocol communication, which can provide a framework for having different channels for inter and intra-node communication.

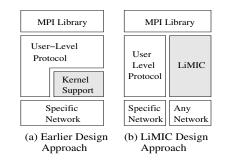

#### CPU Based Kernel Modules for Memory Mapping

Kernel-Based Memory Mapping approach takes help from the operating system kernel to copy messages directly from one user process to another without any additional copy operation. The sender or the receiver process posts the message request descriptor in a message queue indicating its virtual address, tag, etc. This memory is mapped into the kernel address space when the other process arrives at the message exchange point. Then the kernel performs a direct copy from the sender buffer to the receiver application buffer. Thus this approach involves only one copy. Figure 1.2(c) demonstrates the memory transactions needed for copying from the sender buffer directly to the receiver buffer. In step 1, the receiving process needs to bring the sending process' buffer into its cache block. Then in step 3, the receiving process can write this buffer into its own receive buffer. This may generate step 2 based on whether the block was in cache already or not. Then, depending on the cache block replacement policy, step 4 might be generated implicitly.

It is to be noted that the number of possible memory transactions for the Kernel-Based Memory Mapping is always less than the number in User-Space Shared Memory approach. We also note that due to the reduced number of copies to and from various buffers, we can maximize the cache utilization. However, there are other overheads. The overheads include time to trap into the kernel, memory mapping overhead, and TLB flush time. In addition, still the CPU resource is required to perform a copy operation. There are several previous works that adopt this approach, which include [43, 72]. We have explored the kernel based approaches, and implemented a kernel module called LiMIC which will be described in Chapter 4.

#### I/OAT Based Kernel Modules

As mentioned in Section 1.2, DMA based approaches usually have high overhead. Recently, Intel's I/O Acceleration Technology (I/OAT) [44, 57, 68] introduced an asynchronous DMA copy engine within the chip that has direct access to main memory to improve performance and reduce the overheads mentioned above. I/O Acceleration Technology offloads the data copy operation from the CPU with the addition of an asynchronous DMA copy engine. The copy engine is implemented as a PCI-enumerated device in the chipset and has multiple independent DMA channels with direct access to main memory. When the processor requests a block memory copy operation from the engine, it can then asynchronously perform the data transfer with no host processor intervention. When the engine completes a copy, it can optionally generate an interrupt. As mentioned in [44], I/OAT supports several interfaces in kernel space for copying data from a source page/buffer to a destination page/buffer. These interfaces are asynchronous and the copy is not guaranteed to be completed when the function returns. These interfaces return a non-negative cookie value on success, which is used to check for completion of a particular memory operation.

We have designed kernel modules to utilize I/OAT technology for memory copy. The details are described in Chapter 5.

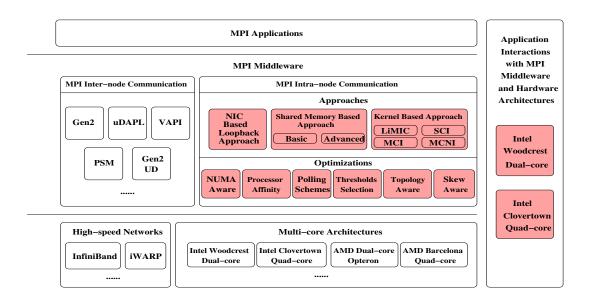

## 1.3 Problem Statement

The scope of this dissertation is shown in Figure 1.3. In short, we aim to design high performance and scalable MPI intra-node communication schemes and study their impacts on applications in-depth. We intend to understand the characteristics of multi-core clusters, and optimize MPI performance on them. In Figure 1.3, the white boxes stand for the existing components, the dark shaded boxes indicate the components we have been working on, and the light shaded boxes are our future work.

We present the problem statement of this dissertation in detail as follows:

• Can we have a significantly better understanding on application characteristics on multi-core clusters, especially with respect to communication performance, message distribution, cache utilization, and scalability? - With the rapid emergence of multi-core architecture, clusters

Figure 1.3: Problem Space of this Dissertation

have entered a multi-core era. In order to get optimal performance, it is crucial to have in-depth understanding on application behaviors and trends on multicore clusters. It is also very important to identify potential bottlenecks in multi-core clusters through evaluation, and explore possible solutions. However, since multi-core is a relatively new technology, few research has been done in the literature.

• Can we design a shared memory based approach to allow MVA-PICH to have better intra-node communication performance? - The original MVAPICH used to use NIC base loopback approach. While it eases code design - we do not need to distinguish between intra- and inter-node communication, the performance is not optimal. Further, with the emergence of multi-core systems, more and more cores can reside within one node, and the NIC based loopback approach may not be scalable since all the intra-node communication will go through the PCI bus and the PCI bus may become a bottleneck. It is essential to have a more efficient intra-node communication scheme.

- Can we optimize the shared memory based approach to have lower latency, better cache utilization, and reduced memory usage, thus have improved performance especially on multi-core clusters? - There are limitations in the current existing shared memory schemes. Some are not scalable with respect to memory usage, and some require locking mechanisms among processes to maintain consistency. Thus the performance is suboptimal for a large number of processes. Moreover, few research has been done to study the interaction between the multi-core systems and MPI implementations. We need to take on the challenges and optimize the current shared memory based schemes to improve MPI intra-node communication performance.

- Can we design MVAPICH intra-node communication to utilize kernel module based approach to reduce the number of copies and potentially benefit applications? - As mentioned in Section 1.2, one approach to avoid extra message copies is to use operating system kernel to provide a direct copy from one process to another. Inside the kernel module, it can either use CPU to do memory copy, or take advantage of any DMA engines that are available for memory copy. Since this kind of approach requires only one memory copy, it may improve MVAPICH intra-node communication

performance. And if we use the DMA for memory copy, we can potentially achieve better computation and communication overlap.

- Can we design an efficient hybrid approach that utilizes both the kernel module based approach and the shared memory based approach to get optimal performance, especially on multi-core clusters? User-level shared memory and kernel assisted direct copy are two popular approaches. Both of them have advantages and disadvantages. However, we do not know if one of these approaches is sufficient for multi-core clusters. In order to obtain optimized performance, it is important to have a comprehensive understanding of these two approaches and combine them effectively.

- What are the factors that affect MVAPICH Intra-node communication and how can we tune them to get the optimal performance?

To optimize communication performance, many MPI implementations such as MVAPICH provide multiple communication channels. These channels may be used either for intra- or inter-node communication. Two important factors that affect application performance are channel polling and threshold selection. It is important to understand how the applications perform with these factors and have efficient channel polling and threshold selection algorithms to improve on performance.

### **1.4** Research Approaches

In this section we present our general approaches to the above mentioned issues.

- Understanding the application characteristics on multi-core clusters

We have designed a set of experiments to study the impact of multi-core architecture on cluster computing. The purpose is to give both application and communication middleware developers insights on how to improve overall performance on multi-core clusters. The study includes MPI intra-node communication characteristics on multi-core clusters, message distribution in terms of both communication channel and message size, cache utilization/potential bottleneck identification, and initial scalability study.

- 2. Designing a basic user-level shared memory based approach for MPI intra-node communication - We have designed a shared memory based implementation for MVAPICH intra-node communication. A temporary file is created and all the processes map the temporary file to their own memory spaces as a shared memory area and use this shared memory area for communication.

- 3. Designing an advanced user-level shared memory based approach for MPI intra-node communication for optimized performance - We have optimized the basic shared memory based design to get better performance and scalability. We want to achieve two goals in our design: 1. To obtain low latency and high bandwidth between processes, and 2. To have reduced memory usage for better scalability. We achieve the first goal by efficiently utilizing the L2 cache and avoiding the use of lock. We achieve the second goal by separating the buffer structures for small and large messages, and using a shared buffer pool for each process to send large messages. We have also

explored various optimization strategies to further improve the performance, such as reducing the polling overhead, etc.

- 4. Designing kernel assisted direct copy approaches to eliminate extra copies and achieve better computation and communication overlap We have designed two major kernel modules for MPI intra-node communication. One is called LiMIC/LiMIC2, which uses CPU based memory copy. And the other uses Intel I/OAT which is an on-chip DMA to do memory copy. We have also modified MVAPICH and MVAPICH2 to utilize the kernel modules.

- 5. Designing an efficient user-level and kernel-level hybrid approach for multi-core clusters - We have carefully considered the characteristics of the shared memory and kernel module based approaches, especially how they perform with multi-core processors. We have analyzed these approaches and come up with a topology-aware and skew-aware approach that combines the two approaches efficiently for multi-core clusters.

- 6. Analyzing factors that affect multi-channel MPI performance and designing optimization schemes Channel polling and threshold selection are two important factors for multi-channel MPI implementations. We have designed efficient polling schemes among multiple channels. We have also explored methodologies to decide the thresholds between multiple channels. We consider latency, bandwidth, and CPU resource requirement of each channel to decide the thresholds.

#### 1.5 Dissertation Overview

We present our research over the next several chapters. In Chapter 2, we present our study of application characteristics on multi-core clusters. We have done a comprehensive performance evaluation, profiling, and analysis using both microbenchmarks and application level benchmarks. We have several interesting observations from the experimental results, including the impact of procesor topology, the importance of MPI intra-node communication, the potential bottlenecks in multi-core systems, and scalability of multi-core clusters.

In Chapter 3, we present our shared memory based designs for MPI intra-node communication. In the shared memory based designs, all the processes map a temporary file to their own memory spaces and use it as a shared memory area for communication. We start with a basic design, in which the buffers are organized such that every process has a receive queue corresponding to every other process. We then present an advance design that reorganizes the communication buffers in a more efficient way so that we can get lower latency, higher bandwidth, and less memory usage.

In Chapters 4 and 5, we take on the challenges and design kernel assisted approaches for MPI intra-node communication. We have designed two major kernel modules, one using CPU based memory copy and other using Intel I/OAT. Both the kernel modules eliminate the extra copies and achieve better performance, and using I/OAT can also achieve better computation and communication overlap.

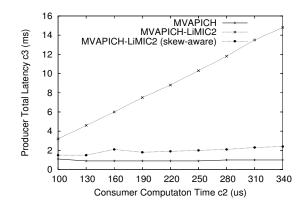

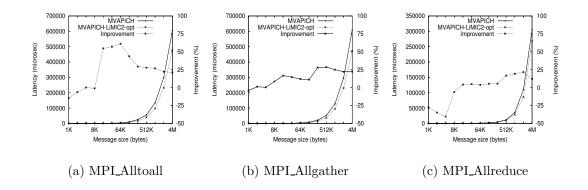

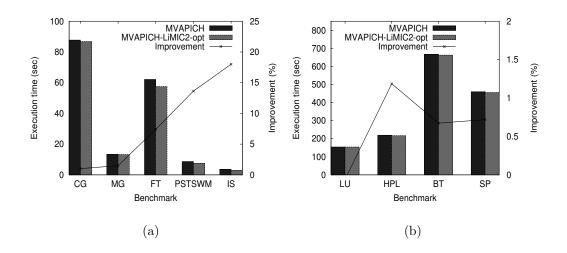

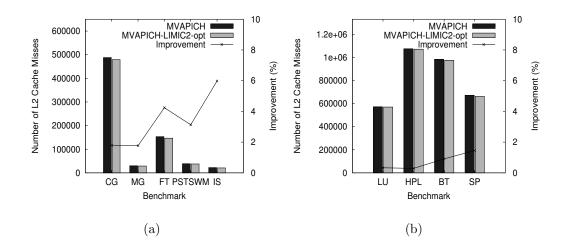

In Chapter 6, we use a three-step methodology to design a hybrid approach for MPI intra-node communication using two popular approaches, shared memory (MVAPICH) and OS kernel assisted direct copy (MVAPICH-LiMIC2). The study has been done on an Intel quad-core (Clovertown) cluster. We have evaluated the impacts of processor topology, communication buffer reuse, and process skew effects on these two approaches, and profiled the L2 cache utilization. And based on the results and analysis we have proposed topology-aware and skew-aware thresholds to build an efficient hybrid approach which shows promising results on multi-core clusters.

Since many MPI implementations utilize multiple channels for communication, in Chapter 7 we have studied important factors to optimize multi-channel MPI. We have proposed several different schemes for polling communication channels, including static polling scheme and dynamic polling scheme. In addition, since multiple channels can be used for MPI intra-node communication, we have also evaluated thresholds for each channel both based on raw MPI latencies and bandwidths and also CPU utilization. These optimizations demonstrate large performance improvement.

## CHAPTER 2

## UNDERSTANDING THE COMMUNICATION CHARACTERISTICS ON MULTI-CORE CLUSTERS

Clusters have been one of the most popular environments in parallel computing for decades. The emergence of multi-core architecture is bringing clusters into a multi-core era. In order to get optimal performance, it is crucial to have in-depth understanding on application behaviors and trends on multi-core clusters. It is also very important to identify potential bottlenecks in multi-core clusters through evaluation, and explore possible solutions. In this chapter, we design a set of experiments to study the impact of multi-core architecture on cluster computing. We aim to answer the following questions:

- What are the application communication characteristics on multi-core clusters?

- What are the potential communication bottlenecks in multi-core clusters and how to possibly avoid them?

- Can multi-core clusters scale well?

The rest of the chapter is organized as follows: In Section 2.1 we describe the methodology of our evaluation. The evaluation results and analysis are presented in Section 2.2. Finally we summarize the results and impact of this work in Section 2.3.

# 2.1 Design of Experiments for Evaluating Multi-core Clusters

To answer the questions mentioned in the beginning of this chapter, we describe the evaluation methodology and explain the design and rational of each experiment.

## 2.1.1 Programming Model and Benchmarks

We choose to use MPI [14] as the programming model because it is the *de facto* standard used in cluster computing. The MPI library used is MVAPICH2 [15]. In MVAPICH2, intra-node communication, including both intra-CMP and inter-CMP, is achieved by user level memory copy.

We evaluate both microbenchmarks and application level benchmarks to get a comprehensive understanding on the system. Microbenchmarks include latency and bandwidth tests. And application level benchmarks include HPL from HPCC benchmark suite [47], NAMD [65] apoal data set, and NAS parallel benchmarks [38].

## 2.1.2 Design of Experiments

We have designed to carry out four sets of experiments for our study: latency and bandwidth, message distribution, potential bottleneck identification, and scalability tests. We describe them in detail below.

- Latency and Bandwidth: These are standard ping-pong latency and bandwidth tests to characterize the three levels of communication in multi-core cluster: intra-CMP, inter-CMP, and inter-node communication.

- Message Distribution: We define message distribution as a two dimensional metric. One dimension is with respect to the communication channel, i.e. the percentage of traffic going through intra-CMP, inter-CMP, and inter-node respectively. The other dimension is in terms of message size. This experiment is very important because understanding message distribution facilitates communication middleware developers, e.g. MPI implementors, to optimize critical communication channels and message size range for applications. The message distribution is measured in terms of both number of messages and data volume.

- Potential Bottleneck Identification: In this experiment, we run application level benchmarks on different configurations, e.g. four processes on the same node, four processes on two different nodes, and four processes on four different nodes. We want to discover the potential bottlenecks in multi-core cluster if any, and explore approaches to alleviate or eliminate the bottlenecks. This will give insights to application writers how to optimize algorithms and/or data distribution for multi-core cluster. We also design an example to demonstrate the effect of multi-core aware algorithm.

- Scalability Tests: This set of experiments is carried out to study the scalability of multi-core cluster.

### 2.1.3 Processor Affinity

In all our experiments, we use *sched\_affinity* system call to ensure the binding of process with processor. The effect of processor affinity is two-fold. First, it eases our analysis, because we know exactly the mapping of processes with processors. And second, it makes application performance more stable, because process migration requires cache invalidation and may degrade performance.

#### 2.2 Performance Evaluation

In this section we present the experimental results and the analysis of the results. We use the format  $p \ge q$  to represent a configuration. Here p is the number of nodes, and q is the number of processors per node.

**Evaluation Platforms:** We use two multi-core clusters and one single-core cluster for the experiments. Their setup is specified below:

Cluster A: Cluster A consists of 4 Intel Bensley systems connected by InfiniBand. Each node is equipped with two sets of dual-core 2.6GHz Woodcrest processor, i.e. 4 processors per node. Two processors on the same chip share a 4MB L2 cache. The overall architecture is similar to that shown in the right box in Figure 1.1. However, Bensley system has added more dedicated memory bandwidth per processor by doubling up on memory buses, with one bus dedicated to each of Bensley's two CPU chips. The InfiniBand HCA is Mellanox MT25208 DDR and the operating system is Linux 2.6.

Cluster B: Cluster B is an Intel Clovertown cluster with 72 nodes. Each node is equipped with dual quad-core Xeon processor, i.e. 8 cores per node, running at 2.0GHz. Each node has 4GB main memory. The nodes are connected by Mellanox InfiniBand DDR cards. The operating system is Linux 2.6.18 We use 32 nodes in Cluster B for our experiments.

Cluster C: Cluster C is a single-core Intel cluster connected by InfiniBand. Each node is equipped with dual Intel Xeon 3.6GHz processor and each processor has a 2MB L2 cache. Cluster C is used to compare the scalability.

In the following sections, Cluster A is used by default unless specified explicitly.

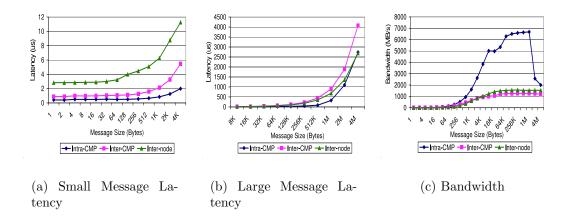

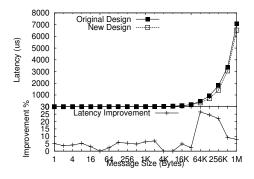

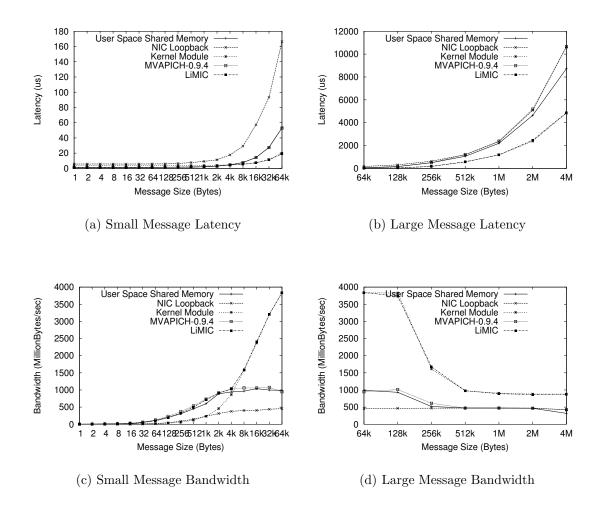

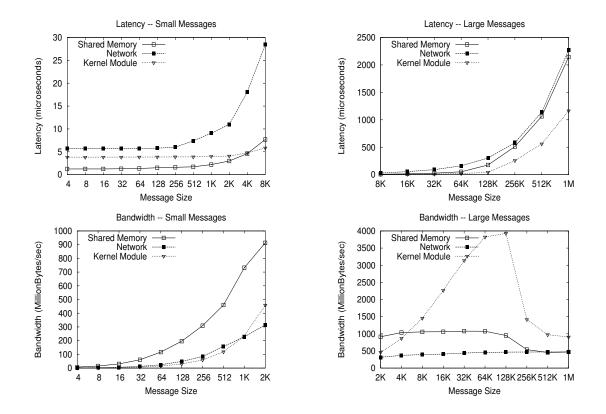

### 2.2.1 Latency and Bandwidth

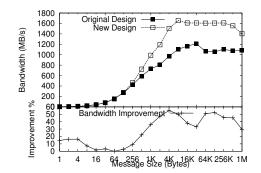

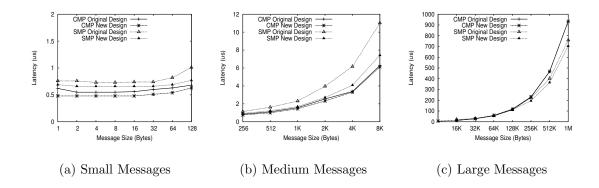

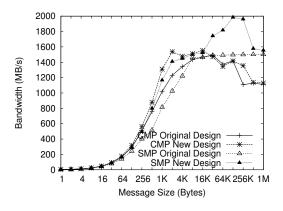

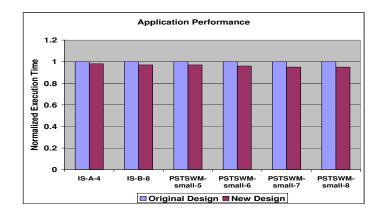

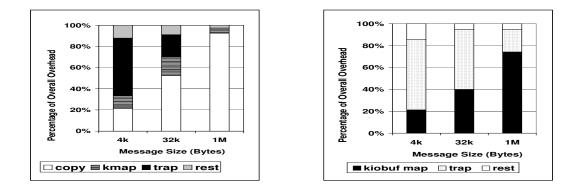

Figure 2.1 shows the basic latency and bandwidth of the three levels of communication in a multi-core cluster. The numbers are taken at the MPI level. The small message latency is 0.42us, 0.89us, and 2.83us for intra-CMP, inter-CMP, and internode communication respectively. The corresponding peak bandwidth is 6684MB/s, 1258MB/s, and 1532MB/s.

From Figure 2.1 we can see that intra-CMP performance is far better than inter-CMP and inter-node performance, especially for small and medium messages. This is because in Intel Bensley system two cores on the same chip share the same L2 cache. Therefore, the communication just involves two cache operations if the communication buffers are in the cache. From the figure we can also see that for large messages, inter-CMP performance is not as good as inter-node performance, although memory performance is supposed to be better than network performance. This is because the intra-node communication is achieved through a shared buffer, where two memory copies are involved. On the other hand, the inter-node communication uses the Remote Direct Memory Access (RDMA) operation provided by InfiniBand and rendezvous protocol [55], which forms a zero-copy and high performance scheme. This also explains why for large messages (when the buffers are out of cache) intra-CMP and inter-node perform comparably.

This set of results indicate that to optimize MPI intra-node communication performance, one way is to have better L2 cache utilization to keep communication buffers in the L2 cache as much as possible, and the other way is to reduce the number of memory copies. We have proposed a preliminary enhanced MPI intranode communication design in our previous work [30].

Figure 2.1: Latency and Bandwidth in Multi-core Cluster

## 2.2.2 Message Distribution

As mentioned in Section 2.1, this set of experiments is designed to get more insights with respect to the usage pattern of the communication channels, as well as the message size distribution. In this section, we first present the results measured on Cluster A and then present the results on Cluster B.

Figure 2.2: Message Distribution of NAMD on 16 Cores

Figure 2.3: Message Distribution of HPL on 16 Cores

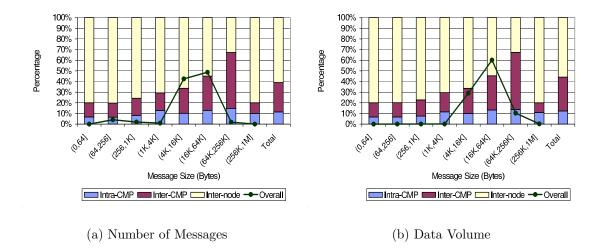

Message Distribution on Cluster A: Figures 2.2 and 2.3 show the profiling results for NAMD and HPL respectively. The results for NAS benchmarks are listed in Table 6.1. The experiments are carried out on a 4x4 configuration and the numbers are the average of all the processes.

Figures 2.2 and 2.3 are interpreted as the following. Suppose there are n messages transferred during the application run, in which m messages are in the range (a, b]. Also suppose in these m messages, m1 are transferred through intra-CMP, m2 through inter-CMP, and m3 through inter-node. Then:

- Bar Intra-CMP(a, b] = m1/m

- Bar Inter-CMP(a, b] = m2/m

- Bar Inter-node(a, b] = m3/m

- Point Overall(a, b] = m/n

From Figure 2.2 we have observed that most of the messages in NAMD are of size 4KB to 64KB. Messages in this range take more than 90% of the total number of messages and byte volume. Optimizing medium message communication is important to NAMD performance. In the 4KB to 64KB message range, about 10% messages are transferred through intra-CMP, 30% are transferred through inter-CMP, and 60% are transferred through inter-node. This is interesting and kind of surprising. Intuitively, in a cluster environment intra-node communication is much less than inter-node communication, because a process has much more inter-node peers than intra-node peers. E.g. in our testbed, a process has 1 intra-CMP peer, 2 inter-CMP peers, and 12 inter-node peers. If a process has the same chance to communicate with every other process, then theoretically:

- Intra-CMP = 1/15 = 6.7%

- Inter-CMP = 2/15 = 13.3%

- Inter-node = 12/15 = 80%

If we call this distribution *even distribution*, then we see that intra-node communication in NAMD is well above that in even distribution, for almost all the message sizes. Optimizing intra-node communication is as important as optimizing inter-node communication to NAMD.

From Figure 2.3 we observe that most messages are small messages in HPL, from 256 bytes to 4KB. However, with respect to data volume messages larger than 256KB take more percentage. We also find that almost all the messages are transferred through intra-node in our experiment. However, this is a special case. In HPL, a process only talks to processes on the same row or column with itself. In our 4x4 configuration, a process and its row or column peers are always mapped to the same node, therefore, almost all the communication take place within a node. We have also conducted the same experiment on a 32x8 configuration for HPL. The results are shown later in this section.

Table 6.1 presents the total message distribution in NAS benchmarks, in terms of communication channel. Again, we see that the amount of intra-node (intra-CMP and inter-CMP) communication is much larger than that in even distribution for most benchmarks. On an average, about 50% messages going through intra-node communication. This trend is not random. It is because most applications have certain communication patterns, e.g. row or column based communication, ring based communication, etc. which increase the intra-node communication chance. Therefore, even in a large multi-core cluster, optimizing intra-node communication is critical to the overall application performance.

| metric   | bench.              | intra-cmp | inter-cmp | inter-node |

|----------|---------------------|-----------|-----------|------------|

| number   | IS                  | 13%       | 18%       | 69%        |

| of       | FT                  | 9%        | 16%       | 75%        |

| messages | CG                  | 45%       | 45%       | 10%        |

|          | MG                  | 32%       | 32%       | 36%        |

|          | BT                  | 1%        | 33%       | 66%        |

|          | SP                  | 1%        | 33%       | 66%        |

|          | LU                  | 1%        | 50%       | 49%        |

| data     | IS                  | 7%        | 13%       | 80%        |

| volume   | $\mathbf{FT}$       | 7%        | 13%       | 80%        |

|          | CG                  | 36%       | 37%       | 27%        |

|          | MG                  | 25%       | 25%       | 50%        |

|          | BT                  | 0         | 33%       | 67%        |

|          | $\operatorname{SP}$ | 0         | 33%       | 67%        |

|          | LU                  | 0         | 50%       | 50%        |

Table 2.1: Message Distribution in NAS Benchmarks Class B on 16 Cores

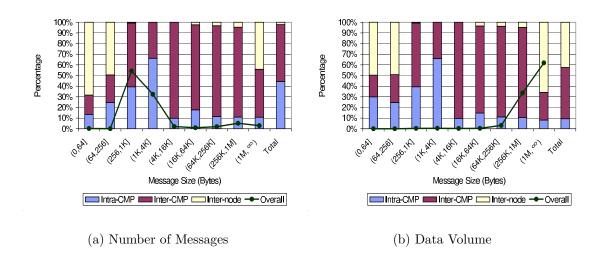

Message Distribution on Cluster B: Figure 2.4 shows the message distribution of HPL on Cluster B with a 32x8 configuration. In this configuration, the even distribution is calculated as follows:

- Intra-CMP = 1/255 = 0.4%

- Inter-CMP = 7/255 = 2.7%

- Inter-node = 248/255 = 96.1%

From the experimental results we see that the percentage of intra-node traffic is much higher than that in even distribution. The overall message distribution during HPL execution is summarized as the follows:

- Intra-CMP = 15.4% (number of messages), 3.5% (data volume)

- Inter-CMP = 42.6% (number of messages), 19.9% (data volume)

- Inter-node = 42.0% (number of messages), 76.6% (data volume)

The NAS message distribution on Cluster B is shown in Table 2.2 which shows the same trend that the intra-node traffic is much higher than that in even distribution for many applications. From this set of experiments we can conclude that even in a large cluster, intra-node communication plays a critical role.

(a) Number of Messages

(b) Data Volume

Figure 2.4: Message Distribution of HPL on 256 Cores

| metric   | bench.        | intra-cmp | inter-cmp | inter-node |

|----------|---------------|-----------|-----------|------------|

| number   | IS            | 1%        | 4%        | 95%        |

| of       | $\mathbf{FT}$ | 1%        | 3%        | 96%        |

| messages | CG            | 23%       | 47%       | 30%        |

|          | MG            | 15%       | 32%       | 53%        |

|          | BT            | 0%        | 29%       | 71%        |

|          | SP            | 0%        | 29%       | 71%        |

|          | LU            | 0%        | 47%       | 53%        |

| data     | IS            | 1%        | 4%        | 95%        |

| volume   | $\mathbf{FT}$ | 1%        | 2%        | 97%        |

|          | CG            | 20%       | 41%       | 39%        |

|          | MG            | 20%       | 19%       | 61%        |

|          | BT            | 0         | 29%       | 71%        |

|          | SP            | 0         | 29%       | 71%        |

|          | LU            | 0         | 47%       | 53%        |

Table 2.2: Message Distribution in NAS Benchmarks Class C on 256 Cores

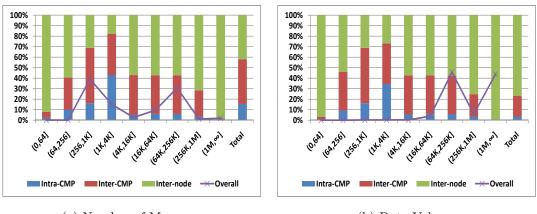

Figure 2.5: Application Performance on Different Configurations

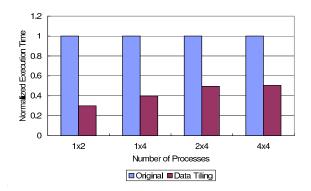

Figure 2.6: Effect of Data Tiling

## 2.2.3 Potential Cache and Memory Contention

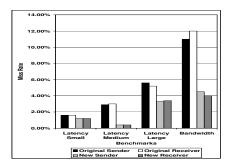

In this experiment, we run all the benchmarks on 1x4, 2x2, and 4x1 configurations respectively, to examine the potential bottleneck in the system. As mentioned in the beginning of Section 2.2, we use the format pxq to represent a configuration, in which p is the number of nodes, and q is the number of processors per node. The results are shown in Figure 2.5(a). The execution time is normalized to that on 4x1 configuration.

One of the observations from Figure 2.5(a) is that 1x4 configuration does not perform as well as 2x2 and 4x1 configurations for many applications, e.g. IS, FT, CG, SP, and HPL. This is because in 1x4 configuration all the cores are activated for execution. As described earlier, on our evaluation platform, two cores on the same chip share the L2 cache and memory controller, thus cache and memory contention is a potential bottleneck. Memory contention is not a problem for processors on different chips, because Intel Bensley system has dedicated bus for each chip for higher memory bandwidth. This is why 2x2 and 4x1 configurations perform comparably. The same trend can be observed from Figure 2.5(b). In this experiment, we run 2 processes on 2 processors from the same chip, 2 processors across chips, and 2 processors across nodes respectively. We see that inter-CMP and inter-node performance are comparable and higher than intra-CMP. The only special case is IS, whose inter-CMP performance is noticeably lower than inter-node. This is because IS uses many large messages and inter-node performs better than inter-CMP for large messages as shown in Figure 2.1.

This set of experiments indicates that to fully take advantage of multi-core architecture, both communication middleware and applications should be multicore aware to reduce cache and memory contention. Communication middleware should avoid cache pollution as much as possible, e.g. increase communication buffer reuse [30], use cache bypass memory copy [28], or eliminate intermediate buffer [49]. Applications should be optimized to increase data locality. E.g. Data tiling [51] is a common technique to reduce unnecessary memory traffic. If a large data buffer is to be processed multiple times, then instead of going through the whole buffer multiple times, we can divide the buffer into smaller chunks and process the buffer in a chunk granularity so that the data chunks stay in the cache for multiple operations. We show a small example in the next section to demonstrate how data tiling can potentially improve application performance on multi-core system.

## 2.2.4 Benefits of Data Tiling

To study the benefits of data tiling on multi-core cluster, we design a microbenchmark, which does computation and communication in a ring-based manner. Each process has a piece of data (64MB) to be processed for a number of iterations. During execution, each process computes on its own data, sends them to its right neighbor and receives data from its left neighbor, and then starts another iteration of computation. In the original scheme, the data processed in the original chunk size (64MB) while in the data tiling scheme, the data are divided in to smaller chunks in the size of 256KB, which can easily fit in L2 cache.

Figure 2.6 shows the benefits of data-tiling, from which we observe that the execution time reduced significantly. This is because in the tiling case, since the intra-node communication is using CPU-based memory copy, the data are actually preloaded into L2 cache during the communication. In addition, we observe that in the cases where 2 processes running on 2 cores on the same chip, since most communication happens in L2 cache in data tiling case, the improvement is most significant, around 70% percent. The improvement in the case where 4 processes running on 4 cores on the same node, 8 processes running on 2 nodes, and 16 processes running on 4 nodes is 60%, 50%, and 50% respectively. The improvements are not as large as that in the 2 process case because the communication of inter-CMP and inter-node is not as efficient as the intra-CMP for 256KB message size.

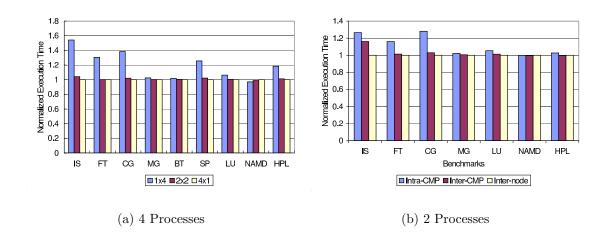

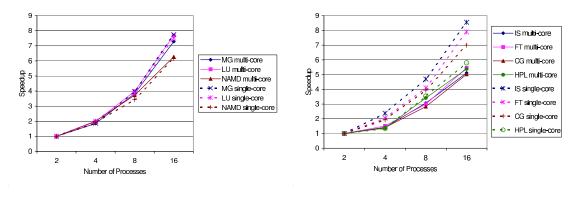

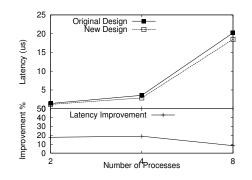

### 2.2.5 Scalability

In this section we present our initial results on multi-core cluster scalability. We also compare the scalability of multi-core cluster with that of single-core cluster. The results are shown in Figure 2.7. It is to be noted that the performance is normalized to that on 2 processes, so 8 is the ideal speedup for the 16 process case.

It can be seen from Figure 2.7(a) that some applications show almost ideal speedup on multi-core cluster, e.g. LU and MG. Compared with single-core cluster

(a) MG, LU, and NAMD

(b) IS, FT, CG, and HPL

Figure 2.7: Application Scalability

scalability, we find that for applications that show cache or memory contention in Figure 2.5(a), such as IS, FT, and CG, the scalability on single-core cluster is better than that on multi-core cluster. For other applications such as MG, LU and NAMD, multi-core cluster shows the same scalability as single-core cluster. As an initial study we find that multi-core cluster is promising in scalability.

## 2.3 Summary

In this chapter we have done a comprehensive performance evaluation, profiling, and analysis on multi-core cluster, using both microbenchmarks and application level benchmarks. We have several interesting observations from the experimental results that give insights to both application and communication middleware developers. From microbenchmark results, we see that there are three levels of communication in a multi-core cluster with different performances: intra-CMP, inter-CMP, and inter-node communication. Intra-CMP has the best performance because data can be shared through L2 cache. Large message performance of inter-CMP is not as good as inter-node because of memory copy cost. With respect to applications, the first observation is that counter-intuitively, much more intra-node communication takes place in applications than that in even distribution, which indicates that optimizing intra-node communication is as important as optimizing inter-node communication in a multi-core cluster. Another observation is that when all the cores are activated for execution, cache and memory contention may prevent the multicore system from achieving best performance, because two cores on the same chip share the same L2 cache and memory controller. This indicates that communication middleware and applications should be written in a multi-core aware manner to get optimal performance. We have demonstrated an example on application optimization technique which improves benchmark performance by up to 70%. Compared with single-core cluster, multi-core cluster does not scale well for applications that show cache/memory contention. However, for other applications multi-core cluster has the same scalability as single-core cluster.

## CHAPTER 3

## SHARED MEMORY BASED DESIGN

As mentioned in Section 1.2, there exist several mechanisms for MPI intra-node communication, including *NIC-based loopback*, *kernel-assisted memory mapping*, and *user space memory copy*.

The user space memory copy scheme has several advantages. It provides much higher performance compared to NIC-based loopback. In addition, it is portable across different operating systems and versions. Due to these advantages, in this chapter we present our shared memory based designs.

The rest of the chapter is organized as follows: In Section 3.1 we describe the basic design of our shared memory based approach. We present the advanced design in Section 3.2 which improves both performance and memory usage over the basic design. The evaluation results and analysis are presented in Section 3.3. Finally we summarize the results and impact of this work in Section 3.4.

# 3.1 Basic Shared Memory Based Design

In this section we describe the basic shared memory based design and optimizations for MVAPICH.

Figure 3.1: Basic Shared Memory Based Design

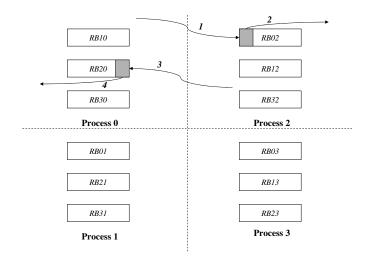

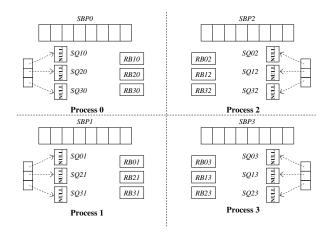

## 3.1.1 Design

The shared memory area is essentially a temporary file created by the first process on a node. The file name consists of the host name, the process id, and the user id, so that multiple jobs submitted by different users can run simultaneously on a node. Then all the processes map the shared memory area to their own memory space by calling mmap() system call. The shared memory area is then used for communication among local processes.

The shared memory area is essentially used as a FIFO queue. The sender writes data to the queue and the receiver reads data from the queue. There are two volatile variables that indicate how many bytes have been written to the queue and how many have been read out of the queue. The sender and the receiver change the values of these two variables respectively. The receiver polls on these two variables from time to time to detect incoming messages. If they do not match it indicates there are new data written to the queue and it can pull the data out. Message matching is performed based on *source rank*, *tag*, and *context id* which identifies the communicator. Message ordering is ensured by the memory consistency model and use of memory barrier if the underlying memory model is not consistent.